5100 是一款多功能的单片网络接口芯片,内部集成有 10/100Mbps 以太网控制器,主要应用于高集成、高稳定、高性能和低成本的嵌入式系统中。使用 W5100 可以实现没有操作系统的 Internet 连接。W5100与 IEEE802.3 10BASE-T和 802.3u 100BASE-TX兼容。W5100 内部集成了全硬件的、且经过多年市场验证的 TCP/IP 协议栈、以太网介质传输层(MAC)和物理层(PHY)。全硬件TCP/IP协议栈支持 TCP,UDP,IPv4,ICMP,ARP,IGMP 和 PPPoE,这些协议已经在很多领域经过了多年的验证。W5100 内部还集成有 16KB存储器用于数据传输。使用W5100不需要考虑以太网的控制,只需要进行简单的端口编程。

与MCU的接口

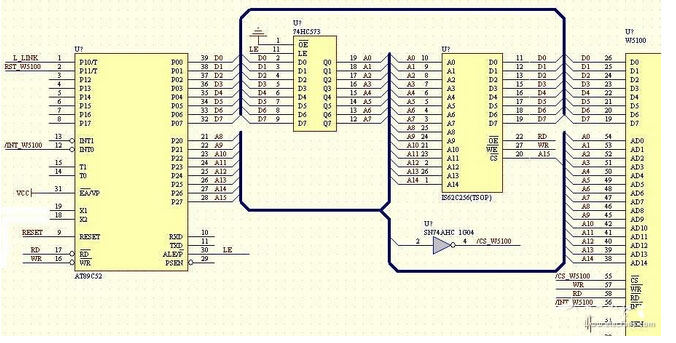

W5100与MCU接口采用并行总线方式(如果要使用SPI接口,建议采用W5200),因此W5100与MCU的接口设计相对简单。以AT89C52为例,如下图所示。

外扩一个32K的SRAM(IS62C256),按照图示的硬件接口,地址线A15作为SRAM的片选信号。因此32K的XDATA地址空间在0×0000~0x7FFF。W5100作为外部接口也映射到89C52的XDATA空间,地址线A15反相(74AHC1G04)后作为W5100的片选信号。因此W5100的地址空间在0×8000~0xFFFF。如果使用间接总线,地址线A2~A14必须接地,以保证间接总线初始化成功。

复位信号

W5100硬件设计中最重要的复位信号往往被我们所忽视。很多工程师采用RC复位,虽然可以达到复位的效果,但实际使用时很不理想。W5100的复位不好往往引起器件不能正常工作,尤其是以太网的物理层不能正常启动,也可能引起MCU对W5100初始化失败。最理想的复位方法是使用MCU的IO口输出复位信号。这样可以绝对保证W5100与MCU之间的同步,而且一旦工作失败,也便于MCU对W5100进行控制。如果MCU无法提供足够多的IO口输出复位信号,也可以采用专用的复位芯片(如IMP809T),这样可以保证可靠复位,但在设计MCU软件时,注意MCU对W5100的操作同步问题。

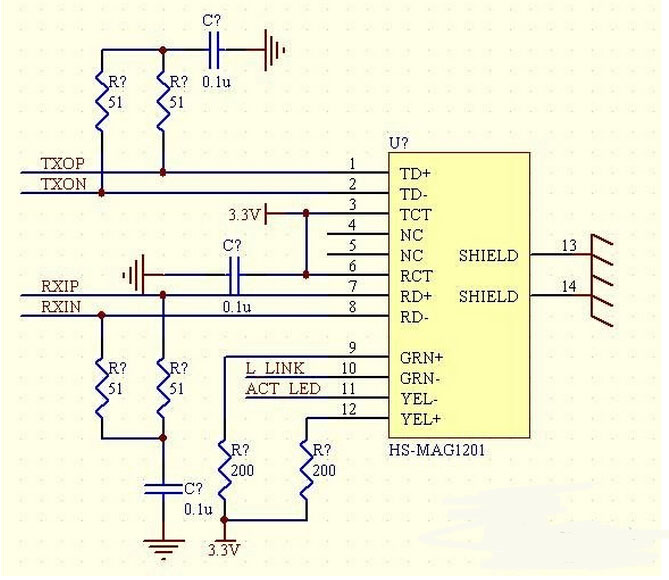

如何连接网络变压器或RJ45

HS-MAG1201是带网络变压器的RJ-45,以此为例,TCT和RCT是变压器发送端和接收端的中心抽头,中心抽头必须接3.3V拉高。很多工程师在设计时忽略了这个细节。另外,RJ-45的金属外壳最好不要接电源地,有条件的话最好接大地。TXOP/TXON,RXIP/RXIN的PCB布线尽量等长,而且尽量平行走线。RSET_BG的电阻连接到W5100的第1脚的RSET_BG电阻最好用1%的精密电阻,尤其是在大批量生产时,使用普通精度的电阻(5%)会给你的产品调试带来意想不到的麻烦。

电感

数字电源到模拟电源之间的电感非常重要。因为从该电感通过的电流比较大,如果电感质量不好,会产生较大的直流压降和交流噪声,严重影响W5100的工作。有很多工程师在初期调试时都遇到过这种问题。如果没有合适的电感,可以把电感去掉,直接用导线短路。

晶体振荡

晶体振荡出现的问题最多,也最难解决。

W5100(W5300和W7100与W5100相同)的晶体振荡器有问题,问题主要表现在:

1. 振荡频率偏差较大,远远偏离25MHz;

2. 振荡幅值不够,XTLN和XTLP的最大幅度只有几百毫伏。

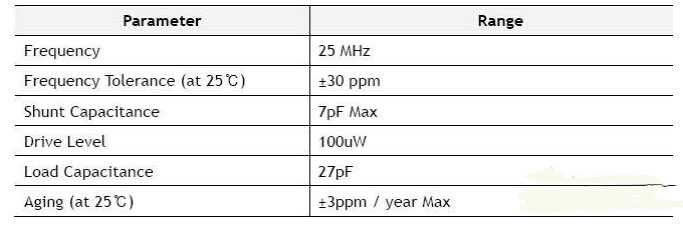

出现这种现象,主要问题是晶体,WIZnet给出的晶体参数如

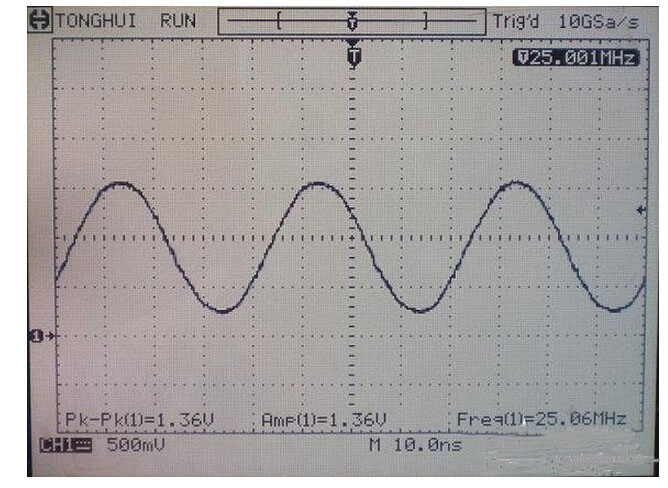

W5100的XTLN的正常波形和幅度如下:

W5100的XTLP的正常波形和幅度如下: