摘要: 为了在不增加CPU工作负担的前提下,实现标准键盘和矩阵键盘双键盘同时工作,提出了一种基于复杂可编逻辑器件(CPLD)的矩阵键盘扫描方案,实现了在矩阵键盘状态控制下CPLD 自动完成键盘扫描、编码、输出的功能,CPU 通过定时器中断服务程序定时查询矩阵键盘状态,并将按键值直接送入键盘缓冲区,供其他程序使用。

给出了CPLD 部分模块的VHDL 语言实现和仿真波形。在矩阵键盘的扫描、编码、输出完全不需CPU 控制的前提下,实现标准键盘和矩阵键盘双键盘同时使用。

在基于PC104 的便携式野外测试设备的设计中,键盘是常用的输入设备。对于便携式设备野外工作时,一般使用小型(4×4)矩阵键盘就能满足设备的信息输入需要; 室内调试时, 使用标准PS2 键盘更方便、灵活。一般的做法是保留PC104 的键盘接口用于接标准键盘, 利用扩展I/O接口完成小矩阵键盘的扫描和输入。这样做虽然可以实现设备双键盘同时工作的功能, 却需耗费大量的CPU 处理时间扫描矩阵键盘, 造成CPU 处理其他信息的能力下降。而本文设计的基于CPLD 的矩阵键盘扫描模块能够很好地解决上述问题。

1 矩阵键盘扫描原理

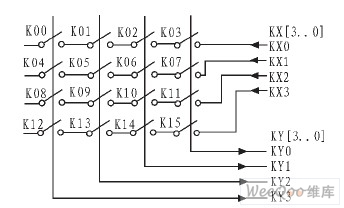

图1 给出了4×4 矩阵键盘的电路图, 在图1 中KX[3..0]为扫描码输入,KY[3..0]为扫描码输出。键盘扫描开始时,首先置KX[3..0]=“0000”;键盘扫描码寄存器和键盘扫描码缓存器Kreg[15..0]和Kscan[15..0]置成“1111111111111111” ( 全1为没有键按下,有键按下时至少有一位为0),一旦有键按下,KY[3..0]输出不全为“0”的扫描码触发键盘扫描功能开始键盘扫描,扫描开始后,依次将KX3、KX2、KX1、KX0 置“0”,分别将对应的4 组KY[3..0]输入值保存于Kscan[15..12]、Kscan[11..8] 、Kscan[7..4] 、Kscan[3..0]中,而后比较Kscan 和Kreg 的大小,如果Kscan 小于Kreg,将Kscan 保存于Kreg 中,重复上述扫描过程直到Kscan[15..0]各位输出全为“1”时,说明按下的键全部抬起,Kreg[15..0]中的每一个为“0”的位对应一个按下的键,保留扫描过程中的Kreg 最小值就可以处理组合键。

根据记录的Kreg 值可以判断是哪个或哪几个键按下, 据此编码按键值后输出。将KX[3..0]置为“0000”,等待下一次按键发生。

图1 4×4 矩阵键盘电路图。

2 基于CPLD 的4×4 矩阵键盘扫描模块设计

根据上述扫描原理和工作流程,如果以PC104 CPU 实现上述矩阵键盘的扫描过程, 那么在有键按下后,CPU 必须不停地扫描矩阵键盘电路,在此期间不能进行其他工作,降低了CPU 工作效率,且CPU 连续高速运转增加系统功耗。

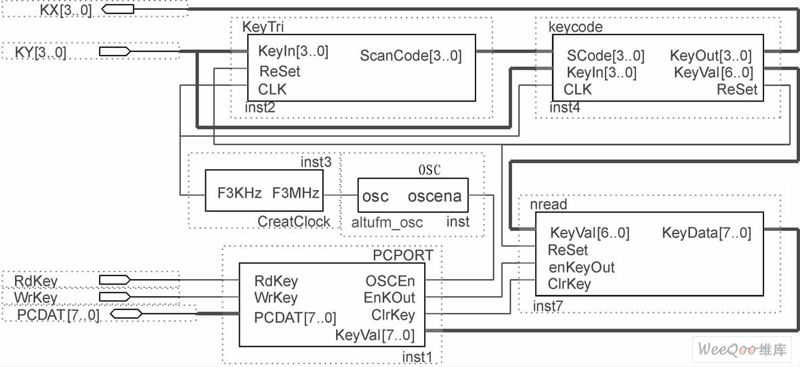

本文的目的就是在不需要CPU 参与的条件下以CPLD完成矩阵键盘按键事件触发、按键的扫描定位以及按键的编码和键值输出工作,CPU 只需要定时查询有无键按下并读走按下键的按键值送入键盘缓冲区。这样就使CPU 从繁重的矩阵键盘扫描工作中解脱出来。根据上述键盘扫描工作原理,基于CPLD 的4×4 矩阵键盘扫描模块功能框图如图2 所示。

图2 4×4 矩阵键盘扫描模块CPLD 实现框图。

图中, 模块KeyTri 在时钟信号CLK 的控制下实现按键事件触发和矩阵键盘扫描时序产生功能; 模块keycode 在时钟信号CLK 和扫描时序码SCode 的控制下完成输出键盘扫描码KX,同时记录16 位键盘扫描数据等工作,并在所有键抬起后对按下的键编码完成输出功能;模块nread 实现按键码的暂存、按键状态的置位和清除以及矩阵键盘的使能;模块PCPORT 完成矩阵键盘与CPU 的接口; 模块OSC 与CreatClock 产生控制键盘扫描模块工作的3 KHz 时钟信号CLK。

2.1 键盘扫描触发模块(KeyTri)的功能与时序仿真

键盘扫描过程中,扫描信号不停变化,以判断键盘按键的按下和抬起。高速变化的键盘扫描信号不仅使系统功耗增加,而且还会对其他敏感电路造成干扰。因此在本设计中将键盘扫描模式设计成键按下触发扫描方式,只有当键盘有键按下后,才触发键盘扫描电路产生扫描键盘时序,所有键都放开后,停止对键盘的扫描,使电路处于相对静止状态,以减少对其他电路的干扰。

键盘按下时会有抖动,在按键抖动时扫描键盘,可能会使键盘扫描电路产生误判,因此在键盘按下与开始扫描之间应加入一段延时,延时结束后按键仍处于按下状态,才允许开始键盘扫描,这样做可以最大限度地避免扫描电路的误判和漏判。

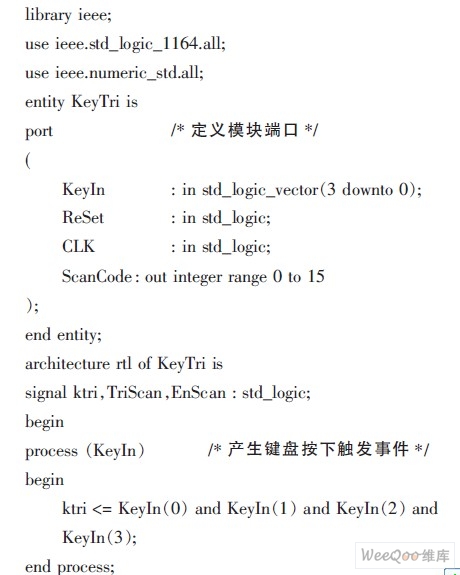

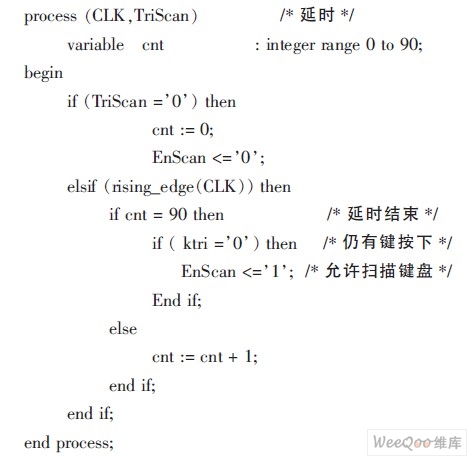

键盘扫描触发模块实现的功能为: 在KX=“0000” 的状态下,如果有任意一个键被按下,KY 必然不全为‘1’,触发延时功能开始延时,延时结束后,如果KY 仍不全为‘1’,说明该按键事件有效, 启动扫描时序产生1H~BH 的4 位循环扫描时序码,控制后续的键盘扫描电路对键盘扫描,当ReSet 变低时,立即将扫描时序码置为0H,停止本次键盘扫描并等待下一次键盘按下事件到来。键盘扫描触发模块的VHDL 语言实现如下:

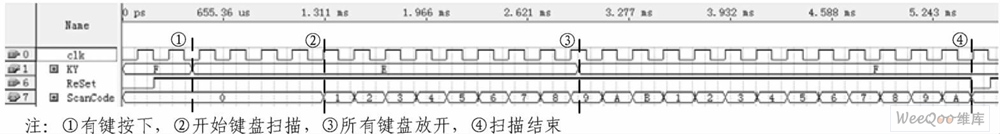

键盘扫描触发模块的时序仿真如图3 所示。

图3 键盘扫描触发模块的时序仿真。

在图3 中,①和②之间的时间为去键盘抖动延时,为了方便仿真,此处把延时时间设定为4 个周期,实际使用时,应保持在20~30 ms 左右。

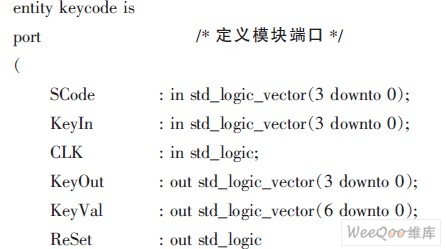

2.2 键盘扫描与编码输出模块(keycode)的功能与时序仿真

所谓键盘扫描,就是在键盘的KX 端依次送入扫描码,以便定位被按下的键。键盘编码是对键盘扫描值译码得到按下键的按键值。

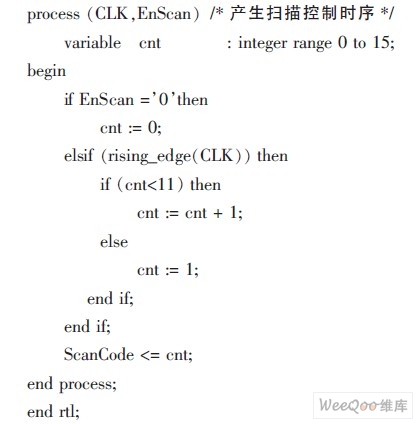

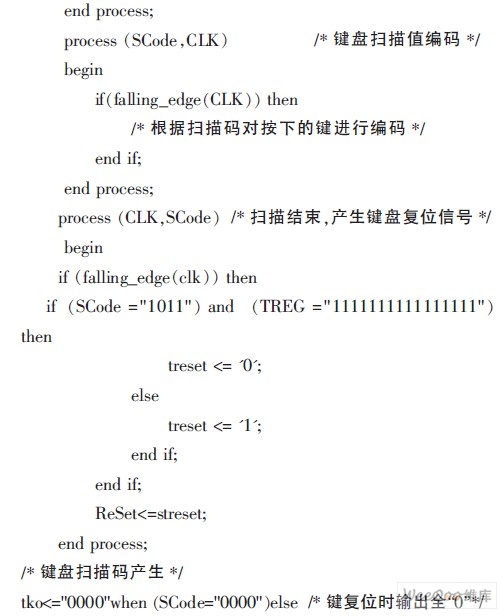

该模块完成的功能为: 在扫描时序控制码SCode [3..0]和CLK 的下降沿控制下依次输出4 组扫描码“0111”、“1011”、“1101”、“1110”扫描整个键盘,同时记录键盘的扫描值,将记录的4 组扫描值组合成一组16 位的键盘扫描值Kscan [15..0],如果Kscan[15..0] 小于Kreg[15..0], 将Kscan[15..0] 保存于Kreg[15..0]中,当所有键放开后,对Kreg[15..0]译码产生按键编码并输出。有一个键按下,16 位的键盘扫描值中有且只有一位为0,多键组合按下时,键盘扫描值中就会有多个位为‘0’,因此在键盘扫描过程中,记录最小的键盘扫描值,使得扫描模块不仅能够处理单键,而且可以处理多键组合。具体工作过程说明如下:

当SCode [3..0]=0 时,KX=“0000”, 置16 位键盘扫描值Kscan[15..0]和Kreg[15..0]为全‘1’,此时无论哪一个键按下,都可使KY 不全为‘1’,从而触发扫描模块工作;当SCode[3..0]=1 或2 时,KX=“0111”,此时图1 中K12~K15 有按下的键时, KY 对应位为‘0’,其他位为‘1’,记录KY到键盘扫描码寄存器的Kreg[15..12];当SCode[3..0]=3 或4 时,KX=“1011”,此时图1 中K08~K11 有按下的键时, KY 对应位为‘0’,其他位为‘1’,记录KY到键盘扫描码寄存器的Kreg[11..8];当SCode[3..0]=5 或6 时,KX=“1101”,此时图1 中K04~K07 有按下的键时, KY 对应位为‘0’,其他位为‘1’,记录KY到键盘扫描码寄存器的Kreg[7..4];当SCode[3..0]=7 或8 时,KX=“1110”,此时图1 中K00~K03 有按下的键时, KY 对应位为‘0’,其他位为‘1’,记录KY到键盘扫描码寄存器的Kreg[3..0];当SCode[3..0]=9 和10 时,如果Kscan[15..0]各位不全为“1” 且Kscan[15..0]< Kreg[15..0], 将Kscan[15..0] 保存到Kreg[15..0];否则对Kreg[15..0]译码产生按键编码并输出;当SCode[3..0]=11 且记录Kscan[15..0]各位为全“1”时,产生键盘复位信号ReSet,结束本次键盘扫描。

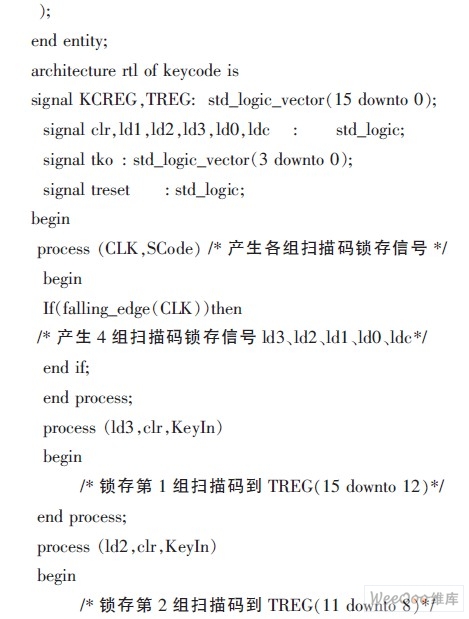

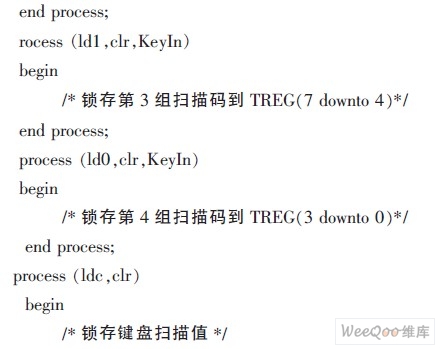

键盘扫描与编码输出模块的核心模块VHDL 语言实现如下:

键盘扫描与编码输出模块的时序仿真图如图4 所示。

图4 键盘扫描与编码模块的时序仿真。

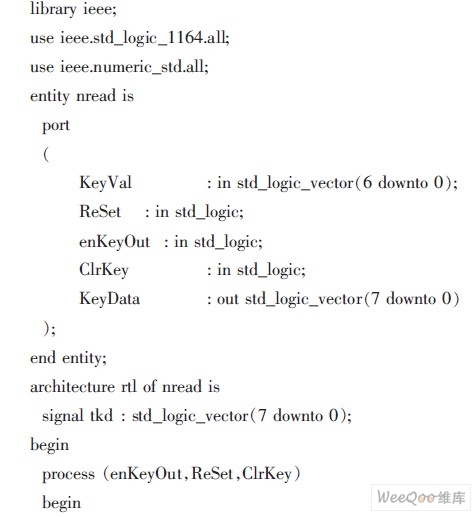

2.3 键盘编码输出模块(nread)的功能与时序仿真

在该模块中,KeyData 的最高位KeyData(7)为键盘缓存状态指示位,当KeyData(7)=‘0’时,表示键盘缓存中没有按键码;当KeyData(7)=‘1’时,表示键盘缓存中有按键码等待CPU 读取。KeyData[6..0]为按下键的编码。ReSet 的下降沿用于将KeyVal[6..0]存入KeyData[6..0],同时将KeyData(7)置成‘1’。enKeyOut 用于使能矩阵键盘输出,当enKeyOut=‘1’时,允许矩阵键盘输出按键码;当enKeyOut=‘0’时,禁止矩阵键盘输出按键码。ClrKey 用于清除键盘缓存状态指示位KeyData(7),当ClrKey=‘0’时,置KeyData(7)为‘0’。

键盘编码输出模块的VHDL 语言实现如下:

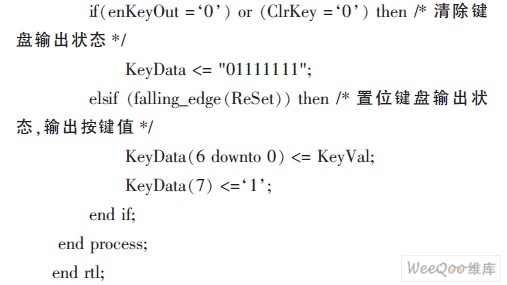

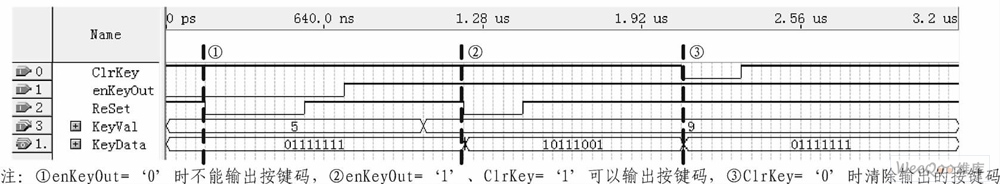

键盘编码输出模块的时序仿真图如图5 所示。

图5 键盘编码输出模块的时序仿真。

2.4 接口模块(PCPORT)的功能与时序仿真

该模块用于实现CPU 读入键盘码以及矩阵键盘控制信号的输出。开始时,CPU 首先应通过该模块送出OSCEn=‘1’ 信号, 使振荡器模块(OSC) 和时钟产生模块(CreatClock)开始工作,产生驱动扫描模块工作的时钟信号F3kHz;接下来送出键盘禁止信号enKeyOut=0;禁止矩阵键盘在稳定工作前随机输出按键值; 其次送出清除键盘缓存状态指示位的ClrKey 信号; 最后再送出键盘使能信号enKeyOut=‘1’,开始模块扫描键盘工作。接口模块的时序仿真图如图6 所示。

图6 接口模块的时序仿真。

2.5 其他模块的功能

振荡器模块(OSC) 为利用Altera 公司的IP 核产生的MAXII 系列CPLD 内带的振荡器, 用于在使能信号的控制下产生3.3 MHz 的时钟输出。

时钟产生模块(CreatClock),用于将3.3 MHz 的时钟分频产生3 KHz 的键盘扫描时钟,驱动整个键盘扫描模块工作。

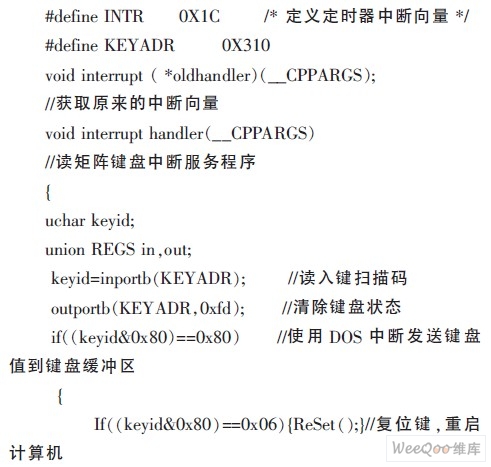

3 控制软件的设计

本文软件设计的基本思想是:CPU 利用定时中断查询矩阵键盘状态并读入矩阵键盘的按键码,如果按键码为需要立即响应的特殊功能键(如热启动键),即在中断服务程序中作出处理,否则直接送入与标准键盘共用的键盘缓冲区,在键盘缓冲区与标准键盘送来的按键码一起排队等待CPU 响应处理,从而实现双键盘同时工作。在向键盘缓冲区写入按键值时,必须使用DOS 软中断,否则会由于中断优先级的原因而使新写入的按键码得不到响应。

矩阵键盘的控制软件采用C 语言编制,利用PC104 的定时器中断定时查询矩阵键盘, 如果有键值, 将其存入PC104 的键盘缓冲区,等待PC104 使用。控制程序的源码如下:

4 测试结果

本文所述的键盘扫描模块已经在多功能电法接收机中使用,在使用过程中对矩阵键盘的响应时间、准确度、CPU 处理时间占用、以及双键盘同时工作性能等指标进行了测试分析,结果如下:

1)矩阵键盘响应时间和准确度测试,理论上计算矩阵键盘的最短响应时间为T=t1+t2+t3+t4=55.9 ms(其中,t1为防抖动延时时间30 ms; t2键盘扫描最短用时, 共扫描2 次用22 个F3 kHz 时钟周期6.6 ms; t3为键盘值暂存时间,3 个F3kHz 时钟周期1 ms; t4为查询键盘中断间隔18.3 ms), 考虑到操作键盘的速度, 测试方法为全部16 个键以3 次/s 的速度连续按6 次,间隔5 s 换一个键,将键值输出到显示器观察输入情况,测试结果为:总按键数:96;显示按键数:96;漏判按键数:0;错判按键数:0;准确率:100%。

2)矩阵键盘占用CPU 时间分析,通过对矩阵键盘按键值的读入程序分析可知, 当允许矩阵键盘输出且有键按下时,每次中断服务程序需要额外执行8 条语句, 大约用时4 μs;当允许矩阵键盘输出且没有键按下时,每次中断服务程序需要额外执行3 条语句,大约用时1.5 μs;与CPU 完成矩阵键盘扫描工作(假设从键按下到释放一般用时300 ms)相比,一次按键读入CPU 占用时间节省99.998%。

3)双键盘同时工作测试,测试方法将矩阵键盘和标准键盘同时接入系统, 按1 次/s 的速度交替按两键盘的按键100个,在显示器上观察按键输出情况,得出双键盘工作可靠性数据如下: 总按键数:200;显示按键数200;漏判按键数:0;错判按键数:0;准确率:100%。因此,该模块可以实现双键盘同时工作。

5 结论

该模块经过测试和使用,得出如下结论:1)基于CPLD 的矩阵键盘扫描模块占用CPU 时间很少;2)可以实现双键盘同时工作;3)误判、漏判率低;4)反应速度快,能够处理组合键。

测试结果表明,该方案满足设计要求。该模块以按键的放开控制按键编码输出,因此在键按下一段时间后到释放按键之前不能按一定的间隔连续输出按下键的键值,矩阵键盘没有连续按键输出功能。键盘码的读入采用PC104 定时器中断(18.3 ms 一次)定时查询的方式实现,在大多数情况下都不会查询到按键事件发生,也就是说矩阵键盘占用的比较少的CPU 处理时间中绝大部分被白白浪费。如果能够修改接口模块实现更灵活的按键外中断触发方式读入键值,还可以节省更多的时间。