VSORA是一家法国巴黎的DSP设计工具公司,推出了一种高效5G宽带新型设计架构,迅速从5G和AI的芯片开发中脱颖而出。近日,创始人兼首席执行官KhaledMaalej和我谈到了VSORA的多核数字信号处理(DSP)知识产权(IP)以及5G和AI应用程序的开发流程。

Maalej和vsora的创始人都来自巴黎的Dibcom(2013年被Parrot收购),该公司为全球领先的低功耗移动电视和无线电接收芯片设计公司。在DiBcom期间,他们注意到高带宽基带系统的技术并没有得到充分发展和提升。他们认为,由于非常不合理的开发流程上的缺陷,往往造成算法工程师和DSP开发人员之间形成一个耗时的反复推翻的因境,大大地拖延了研发周期。

Maalej解释说算法工程师在MATLAB环境中设计一种算法。一旦他们相信他们的建模将提供了令人满意的结果,他们就会固化算法,并将其交给DSP开发人员来实现。DSP小组将花费几个月的时间对算法进行彻底的RTL设计验证。

“在这个阶段,就可能碰到麻烦”Maalej说。首先根据目标规格对DSP设计的总体性能即速度、面积和功耗进行测试,然后DSP开发人员将其交给宽带系统工程师和嵌入式软件开发人员,以便在宽带系统设计中进行部署。当总体性能不符合规范时,研发流程则退回到算法工程师,由算法工程师必须对算法进行再次修正,重新与DSP硬件开发人员之间进行设计迭代。

其结果往往是推迟了宽带设计的发布,增加了无法实现最优化设计的风险。

Maalej指出:“DSP已经存在了几十年,而这些缺陷还没有在设计流程中得到有效解决。”目前的DSP技术没有提供足够的处理能力去满足现今高带宽系统的需求,例如5G无线应用程序。设计者不得不在可编程DSP周围添加DSP协处理器,通过增加硬件方式系统去实现算法。如果设计人员没有在产品规化时为应用程序提供足够的电力,或者功耗超过预计的设计值 ,则必须对其进行修改以满足要求,通过迭代以增加处理能力和降低功耗。

VSORA通过基于多核信号处理器(MSP)的方法,改变DSP硬件设计方案来提供高效的处理能力并降低功耗,增加其可编程的灵活性。

Maalej确信“为了应对大数据的复杂算法,比如应对5G宽带的设计要求,功耗的增加是肯定的” 。VSORA的MSP集成了一个信号管理器来处理硬件中的三维信号矩阵,使用高带宽存储器,以确保嵌入式算术逻辑单元(ALU)得到充分利用。此外,在单个时钟周期中可执行的大量指令加上对每个周期多条指令的支持,以此增加了MSP的处理能力和效率。

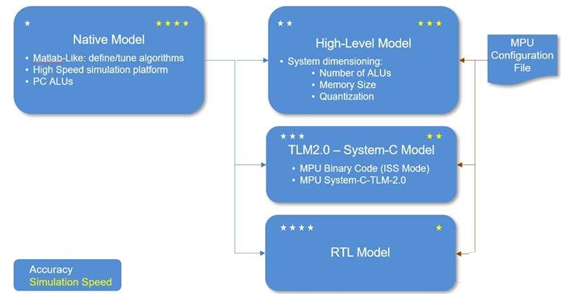

这个开发流程无需生成底层运算代码,方法是将源代码保持在由算法工程师创建的类似matlab语言的格式中。VSORA MSP开发流程自动将源代码编译为在MSP上运行的二进制格式。因此研发者可以轻松地评估算法的速度、面积和功耗。

因此,从算法工程师即可开始控制开发流程,充分展示最终产品的规格。系统成本优化取决于所选择的算法,在项目开始时即可进行评估。算法工程师可以分析不同算法带来的成本,并根据需要重新调整或修改算法,从而简化复杂系统的研发流程。

新的MSP开发流程可以将信号处理代码和系统嵌入式软件代码混合到相同的文件中,供宽带系统工程师和算法工程师交互讨论,系统工程从算法设计开始即可介入项目,以此减少失误和开发节点之间反复。

Maalej说:它类似于软件开发流程。通过从开发流程中排除DSP硬件实现,并让算法工程师完全控制流程,该流程与软件流程相当相似,使其更快、更高效、更便宜。

“复杂的系统不能被集成到单一的核”他补充说。MSP允许算法工程师选择每个任务的内核数和每个处理器的大小,决定每个核心的ALU数以及计算精度。

VSORA的DSP开发流程类似于软件工程师使用的开发流程。

在问及将5G和AI应用程序集成到MSP的复杂系统有多困难时,Maalej说:“一般来说,算法工程师不熟悉技术最终应用场景。这就是我们简化了开发流程并将系统工程从开始即介入的原因,允许他们以一种简单的方式执行实现。他们不需要改变他们的系统模拟去尝试不同的硬件配置,或者改变内核的数量,例如,从三个到四个核。在VSORA设计流程中只需要用两行简单代码中的一行即可进行硬件分配。“

新兴的5G无线网络具有大数据高速率、低延迟、低功耗、低成本、提高系统容量和大规模设备连接的特点。因此,一个更高效的流程来支持DSP开发,以确保5G的成功是非常重要的。