不考虑进位输入时,两数码Xn、Yn相加称为半加器;若考虑低位进位输入Cn-1相加,则称为全加器。全加和Fn和进位输出Cn的表示式分别为:

Fn=XnYnCn-1+ XnYnCn-1+ XnYnCn-1+ XnYnCn-1

Cn= XnYnCn-1+ XnYnCn-1+ XnYnCn-1+ XnYnCn-1

其推导过程和逻辑电路图详见教材19页图26所示。

有关半加器和全加器的功能表及逻辑图如教材中图2.5和图2.6

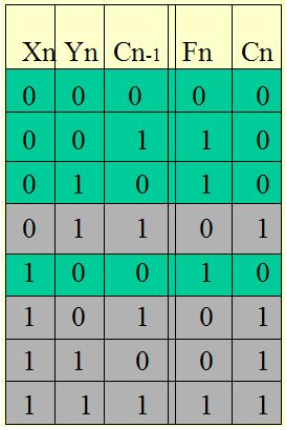

补充一位全加器真值表如右:

其中Xn 为被加数,Yn为加数, Cn-1为低级进位信号,Fn为和,Cn为本级向上进位信号。

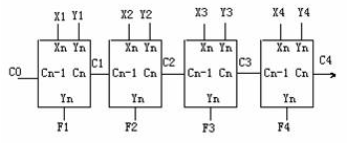

简单串行级联的4位全加器如下图所示: (教材图2-7 四位串行加法器)

将4个全加器相连可得4位加法器(图2.7),但其加法时间长。这是因为其位间进位是串行传送的。本位全加和Fi必须等低位进位Ci-1来到后才能进行,加法时间与位数有关。只有改变进位逐位传送的路径,才能提高加法器工作速度。解决办法之一是采用“超前进位产生电路”来同时形成各位进位,从而实行快速加法。我们称这种加法器为超前进位加法器。根据各位进位的形成条件,可分别写出Ci的逻辑表达式:

C1=X1Y1+(X1+Y1)C0=G1+P1C0 其中:

Gi=Xi·Yi 称为进位产生函数

Pi=Xi+Yi 称为进位传递函数

Gi的意义是:当 XiYi 均为“1”时定会产生向高位的进位

Pi的意义是:当Xi和Yi中有一个为“1”时,若同时低位有进位输入,则本位也将向高位传送进位。写成通用式为:

C1=G1+P1C0 (低位) ( 2.22)

C2=G2+P2C1= G2+P2(G1+P1C0)= G2+P2G1+P2P1C0(2.23)

C3=G3+P3 G2+ P3 P2G1+ P3 P2P1C0 (2.24)

C4=G4+P4 G3+ P4 P3 G2+ P4 P3 P2G1+ P4 P3 P2P1C0 (2.25)

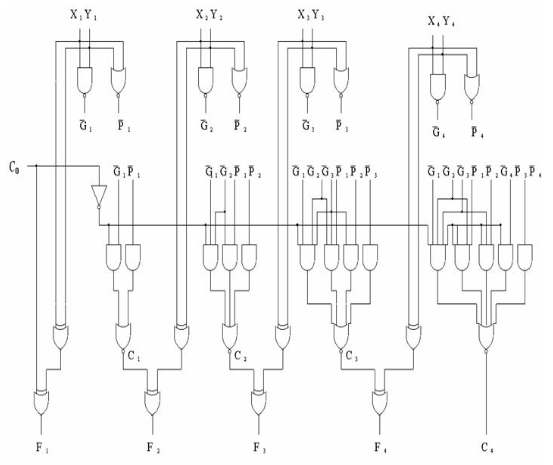

当全加器的输入均取反码时,它的输出也均取反码。(应用反演律采用与非、或非、与或非表示)将上式改写成如下:

C1=P1+G1C0

C2=P2+G2P1+G2G1C0

C3=P3+G3 G2+ G3G2P1+G3G2G1C0

C4=P4+G4P3+G4G3P2+G4G3G2P1+ G4G3G2G1C0

根据上式可画得“超前进位产生电路”及四位超前进位加法器的逻辑图如图2.8。

2.4.2 算术逻辑单元(简称ALU)

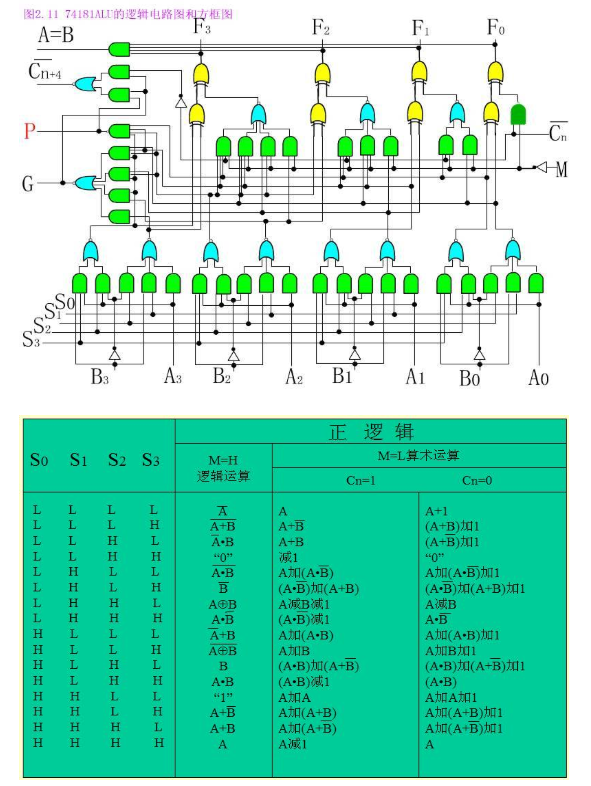

•ALU是一种功能较强的组合逻辑电路。它能进行多种算术运算和逻辑运算。ALU的基本逻辑结构是超前进位加法器,它通过改变加法器的进位产生函数G和进位传递函数P来获得多种运算能力。下面通过介绍SN74181型四位ALU中规模集成电路了介绍ALU的原理。

•在图2.9中功能表中,“加”表示算术加,“+”表示逻辑加。它能执行16种算术运算和16种逻辑运算,M是状态控制端,M=H,执行逻辑运算;M=L执行算术运算。S0 ~S3是运算选择端,它决定电路执行哪种算术运算或逻辑运算。

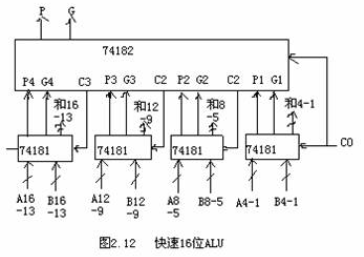

用四片74181电路可组成16位ALU。如下图片内进位是快速的,但片间进位是逐片传递的,因此总的形成时间还是是比较长的。

如果把16位ALU中的每四位作为一组,用类似位间快速进位的方法来实现16位ALU(四片ALU组成),那么就能得到16位快速ALU。推导过程如下:

图 2.10

•与前面讲过的一位的进位产生函数Gi的定义相似,根据四位一组的进位产生函数GN为“1”的条件,可以得到GN的表达式为:

GN =G3+P3G2 +P3P2G1 +P3P2P1G0

•与前面讲过的一位的进位传递函数Pi的定义相似,根据四位一组的进位传递函数PN为“1”的条件,可以得到PN的表达式为:

PN =P3P2P1P0

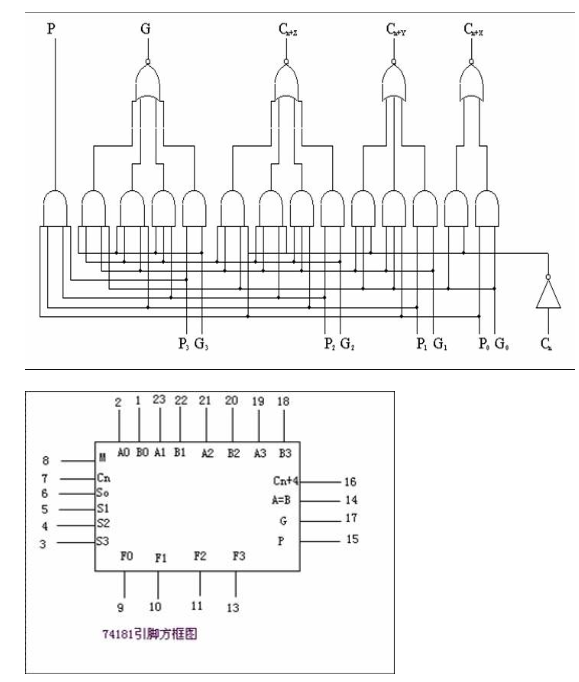

把图2.10各片的进位分别命名为Cn+X 、 Cn+Y 、 Cn+Z (即C3 C7 C11)。根据式2.22~2.25的推导可将式中的G1,G2, G3和P1 P2, P3分别换为 GN0, GN1, GN2和PN0, PN1, PN2,把C0换以Cn,即可得Cn+X 、 Cn+Y 、 Cn+Z 的表示式如下:

Cn+X = GN0 + PN0 Cn= GN0 + PN0Cn= GN0PN0+GN0Cn(2-33)

Cn+y=GN1+PN1GN0+PN1PN0Cn =GN1+PN1GN0+PN1PN0Cn

=GN1PN1+ GN1GN0PN0 +GN1GN0Cn (2-34)

Cn+Z=GN2+PN2 GN1+ PN2 PN1GN0+ PN2 PN1PN0Cn

=GN2+PN2 GN1+ PN2 PN1GN0+ PN2 PN1PN0Cn (2-35)

=GN2PN2 + GN1GN0PN1+GN2GN1GN0Pn0 +GN2GN1GN0Cn

由2-33,2-34,2-35式可知,只要74181型ALU能提供输出GN, PN那么就可用3个与或非门和4片ALU相连,这样就能实现16为快速ALU。

实现2-33,2-34,2-35式的逻辑电路就成为超前进位扩展器(74182芯片),图2-11使它的逻辑电路图,图中将Pni、GNi分别用Pi、Gi表示。图中P、G输出可用于把4组16位快速ALU扩展成64位快速ALU。图2-12画出了用74181和74182芯片构成的16位快速ALU。

图2.11与7418型ALU连用的超前进位产生电路

用两个16位全先行进位部件(74182)和八个74181可级连组成的32位ALU电路

用四个16位全先行进位部件(74182)和十六个74181可级连组成的64位ALU电路

由于集成器件的集成度的提高,允许更多位的ALU集成在一个芯片内。例如AMD公司的AM29332为32位ALU,而在Intel公司的Pentium处理器中,32位ALU仅是芯片内的一部分电路。尽管器件不同,但基本电路原理还是相识的。

2.4.3译码器

译码:把某组编码翻译为唯一的输出,实际应用中要用到的有地址译码器和指令译码器。

译码器:有2—4译码器、3—8译码器(8选1译码器)

和4—16译码器(即16选1译码器)等多种。

书中介绍的是2—4译码器的组成及应用

例如:3—8译码器,即8选1译码器的输入信号有三个:C、B、A(A为低位),三位二进制数可组成8个不同数字,因此可分别选中输出Y0 到Y7的某一个输出故称为 8选1译码器。在资料手册中的型号为74138。

下图分别为译码器引脚图和输入输出真值表

其中:G1、G2A、G2B为芯片选择端,G1高电平有效,而G2A、G2B为低电平有效。

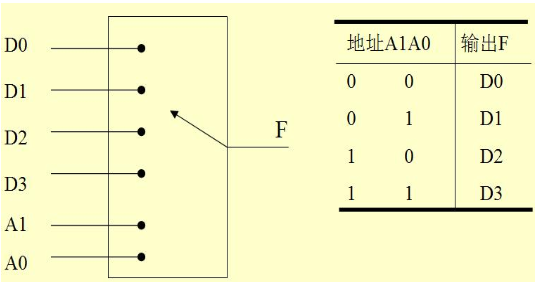

2.4.4 数据选择器

逻辑功能是在地址选择信号的控制下,从多路数据中选择一种作为输出信号。又称多路开关或多路选择器。以四选一选择器为例:

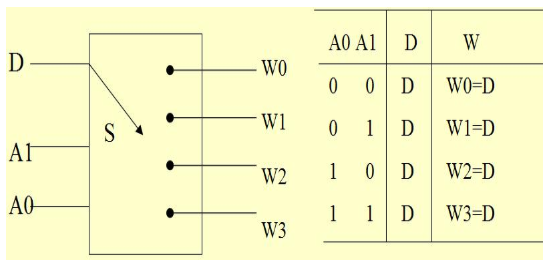

2.4.5 数据分配器

数据传输过程中,常常需要将一路数据分配到多路装置中指定的某一路中,执行这种功能的电路叫数据分配器。下面以四路数据分配器为例进行说明:

2.5 时序电路

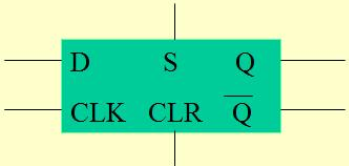

2.5.1 (1) D触发器

电路符号:

D为数据输入端;

CLK为时钟信号;

S为置位信号端;

CLR复位信号端;

Q为输出信号端。

D触发器功能表:

正跳变触发有效。

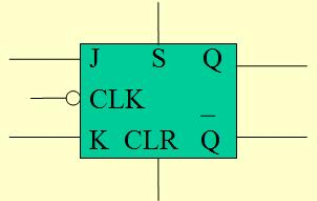

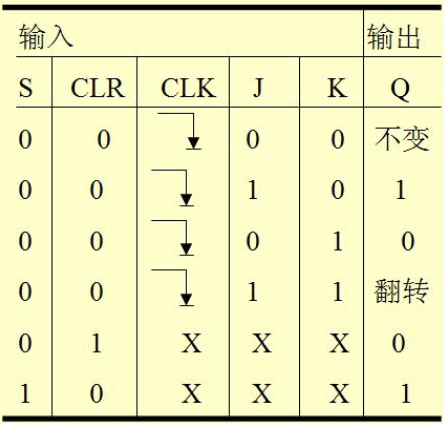

(2)、J-K触发器

电路符号

JK为控制输入端;

CLK为时钟信号;

S为置位信号端;

CLR复位信号端;

Q为输出信号端。

2.5.2-1 寄存器

计算机中常用部件,用于暂存二进制信息。

寄存器可由多个触发器组成。每个触发器存

1Bit,N个触发器储存N位二进制数据。

下图为由4个D触发器组成的四位缓冲寄存器。

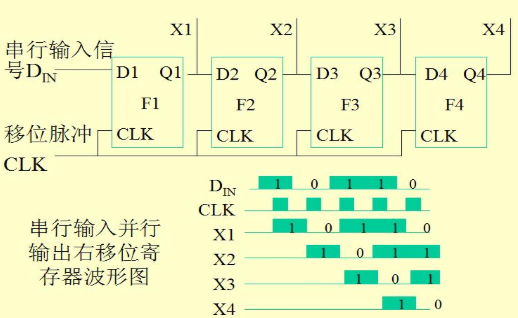

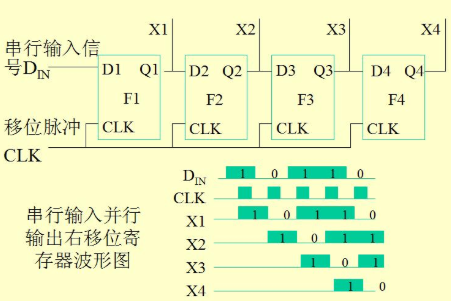

2.5.2-2 移位寄存器

•移位寄存器不仅具有存储数据的功能,而且还具有移位功能。所谓移位功能就是将移位寄存器中所存的数据,在移位脉冲信号的作用下,按要求逐次向左、右方进行移动。

•从信号输入上分有串行输入和并行输入

•从信号输出上分有串行输出和并行输出

•下面以串行输入并行右移位寄存器为例进行说明:

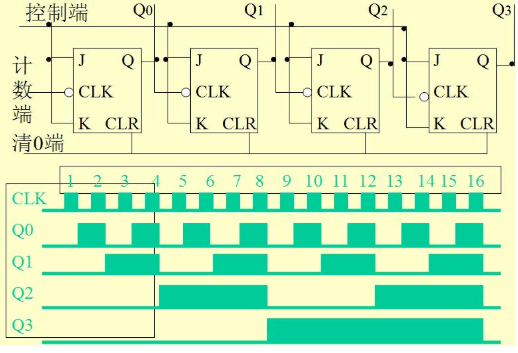

2.5.3、四级二进制并行计数器