LVDS输出接口概述

液晶显示器驱动板输出的数字信号中,除了包括RGB数据信号外,还包括行同步、场同步、像素时钟等信号,其中像素时钟信号的最高频率可超过28MHz。采用TTL接口,数据传输速率不高,传输距离较短,且抗电磁干扰(EMI)能力也比较差,会对RGB数据造成一定的影响;另外,TTL多路数据信号采用排线的方式来传送,整个排线数量达几十路,不但连接不便,而且不适合超薄化的趋势。采用LVDS输出接口传输数据,可以使这些问题迎刃而解,实现数据的高速率、低噪声、远距离、高准确度的传输。

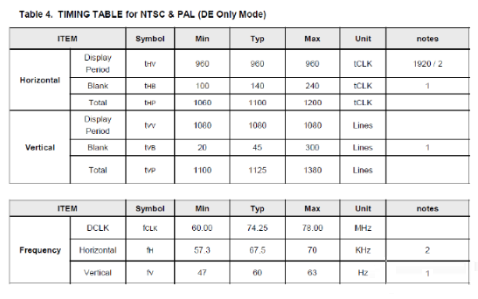

LVDS接口信号驱动原理(1920*1080)一、时钟与像素点关系

一场:60Hz-16.667ms,1125行(1080行有效)

——刷新像素点:1920*1080个/VerTIcal

一行:67.5KHz-14.815us,(=60Hz*1125),1100*2点(1920点=960*2点有效)

——刷新像素点:1920个/ Horizontal

Clock:74.25MHz-13.468ns,(=67.5KHz*1100)

——刷新像素点:2个/Clock

以上,可参考《附录A:屏规格书信号时序特性》。

二、LVDS信号传输规则

以双八位信号接口为例,每个Clock(奇+偶),LVDS接口有4*2对差分对(双8位)同时传输,每4对差分对负责1Pixels;每个Clock(奇+偶)共传输2Pixels;

每4对差分对同时串行传输7*4 =28bits,每对差分对串行传输7bits(每bit周期1.924ns=13.468ns/7)

以上,可参考《附录B:屏规格书LVDS信号时序》与《附录C:屏规格书数据传输格式》。

通常,LVDS接口的时钟为20MHz到85MHz,因此对于输出像素时钟低于85MHz的信号,只需要一个channel就可以;而对于输出像素时钟高于85MHz的信号,比如1080P/60Hz的输出,像素显示时钟为148.5MHz,就不能直接用一个channel传输,而是将输出的像素按照顺序分为奇像素和偶像素,将所有的奇像素用一组LVDS传输,所有的偶像素用另外一组LVDS传输。也就是说,需要两个channel来传输1080P/60Hz的信号。

对于像素显示时钟更高的信号,比如1080P/120Hz显示,则需要4个channel来传输; 以上,可参考《附录D:2 channel、4 channel的像素分配》。

附录A:屏规格书信号时序特性

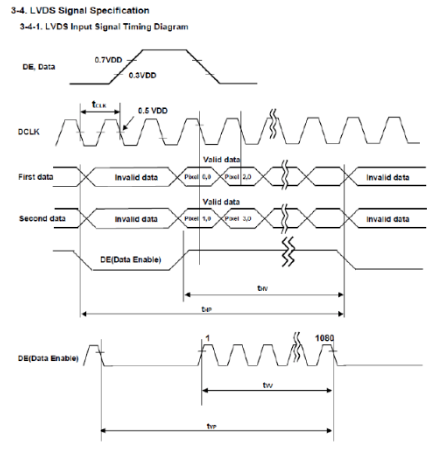

附录B:屏规格书LVDS信号时序

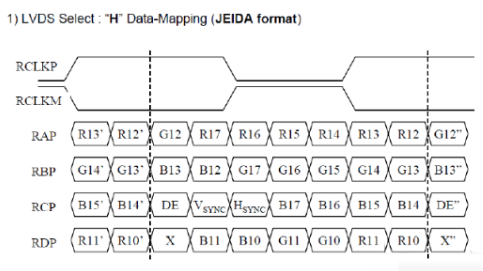

附录C:屏规格书数据传输格式