什么是并行信号?串行信号?

要了解并行信号和串行信号,我们还是来先了解下并行通信(传输)和串行通信(传输)的概念吧。并行信号就是以并行方式通信的信号,而串行信号就是以串行方式通信的信号。串行通信指数据在单条一位宽的传输线上,一比特接一比特地按顺序传送的方式,在早期的定义里也有说只有一根数据线,每个时钟脉冲下只能发送一位数据的方式;而在并行通信中一个字节(8位)数据是在8条并行传输线上同时由源端传到目的地,也可以说有多个数据线(几根就是几位),在每个时钟脉冲下可以发送多个数据位(几位的并行口就发送几位)。

所以早期对串行通信与并行通信的理解为:同样的一个字节数据(8位),串行通信要分8次由低位到高位按顺序一位位地传送,而并行通信由于有8根线路,所以只要一次就可以传送过去,形象的说,把线路(通道)比作道路,能并排开几辆车的就可以说是“并行”,只能一辆一辆开的就属于“串行”了。

并行通信与串行通信的区别对比及优缺点

很明显,并行通信的速度要比串行通信的速度快得多,效率更高,费时更少。不过这些都是早期I/O速率都不高的情况下的理论理解,随着信息技术的飞速发展,之前的理解放在现在来看已经过时了,因为现在是高速串行信号时代了(我们的主题)。

在高速状态下,并行口的几根数据线之间存在串扰,而并行口需要信号同时发送同时接收,任何一根数据线的延迟都会引起问题。而串行只有一根数据线,不存在信号线之间的串扰,而且串行还可以采用低压差分信号,可以大大提高它的抗干扰性,所以可以实现更高的传输速率,尽管并行可以一次传多个数据位,但是时钟远远低于串行,所以目前串行传输是高速传输的首选。

在此套用铁杆粉丝“绝对零度”的回复:“打个比方,运送大型设备零件,并行信号就好比多辆货车,每辆车运送一些零件,大家按一定的时间要求送到目的地才能装配出完整的设备,一辆车出故障就会导致无法完成组装。而串行信号就好比火车,正常情况下一辆车就可以把所有零件运送完毕,而且不会出现问题。”个人觉得这个比喻还是比较恰当的,在这里火车本身也是比货车速度快的。

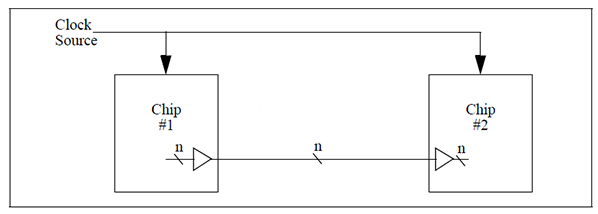

从另外的角度来看,并行传输还有很多方式如系统同步(共同时钟)方式及源同步时钟方式等。先来看系统同步先天的内在问题,下图是并行传输中系统同步方式的示意图。

首先,并行信号由于需要多位传输路径,这在早期是可以接受的。但是摩尔定律的现象使得与几十年前相比可生产的芯片中硅电路的数量大幅增加,而芯片封装技术的pin密度并没有像硅密度一样以相同的速度在增加,因此I/O pin的封装实际上比硅电路还贵,这就意味着对于大多数芯片来说pin管脚越来越多变得不可接受。就好像我们都知道车道越多我们的通行效率就会更快,但随着现在的城市空间越来越小以及地价越来越贵,更多的车道慢慢的只能变得越来越难以实现。况且并行本身的I/O速率不高,就像拖拉机或毛马路,速度上不去再多车道也是枉然。

第二个内在问题就是时序的需求。由上图可知数据由芯片#1同步启动并被芯片#2使用相同的时钟同步捕获,芯片#2输入端的数据必须满足相对于芯片的时钟输入的建立和保持时间。详细的系统同步时序模型如下图所示。

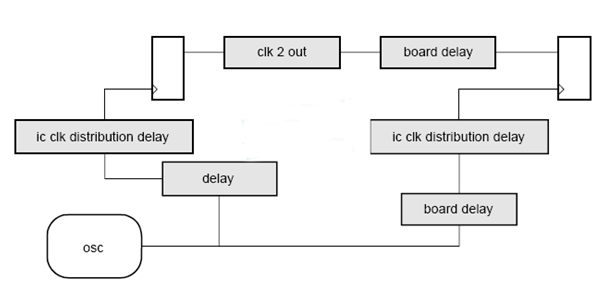

这些建立和保持时间必须用足够的余量来计算,以允许时钟分配路径延迟到两个芯片的差异,并通过芯片到启动和捕捉触发器。延迟可能会因芯片工艺,电压和温度(PVT)条件而异,并且必须增加余量以应对最坏的情况。对于较高的时钟频率,可能需要在芯片中使用锁相环(PLL)来调整时钟相位,以补偿芯片内的时钟分配延迟,并适应变化的工艺,电压和温度条件。 如果时钟频率足够高,则不可能建立一个可以通过这种共同时钟总线来可靠地传输数据的系统。