74LS373是一款常用的地址锁存器芯片,由八个并行的、带三态缓冲输出的D触发器构成。在单片机系统中为了扩展外部存储器,通常需要一块74LS373芯片。本文将介绍74LS373的工作原理。

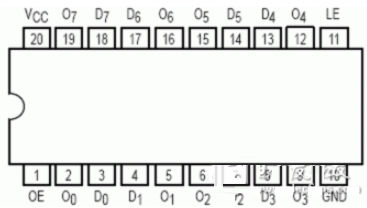

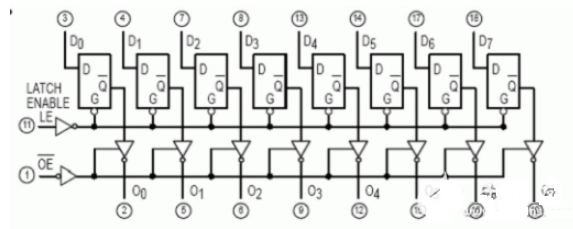

一、74ls373引脚图及功能介绍

G为数据打入端:当G为“1”时, 锁存器输出状态(1Q~8Q)同输入状态(1D~8D);当G由“1”变“0”时,数据打入锁存器中。

二、74ls373工作原理

(1).1脚是输出使能(OE),是低电平有效,当1脚是高电平时,不管输入3、4、7、8、13、14、17、18如何,也不管11脚(锁存控制端,G)如何,输出2(Q0)、5(Q1)、6(Q2)、9(Q3)、12(Q4)、15(Q5)、16(Q6)、19(Q7)全部呈现高阻状态(或者叫浮空状态);

(2)。当1脚是低电平时,只要11脚(锁存控制端,G)上出现一个下降沿,输出2(Q0)、5(Q1)、6(Q2)、9(Q3)、12(Q4)、15(Q5)、16(Q6)、19(Q7)立即呈现输入脚3、4、7、8、13、14、17、18的状态。

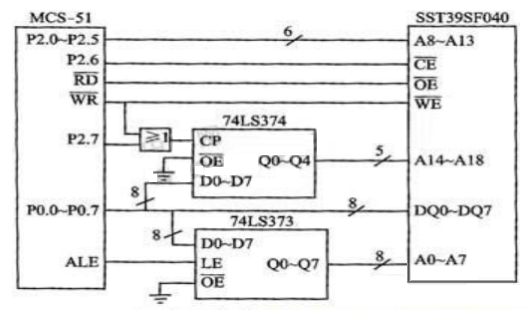

锁存端LE 由高变低时,输出端8 位信息被锁存,直到LE 端再次有效。 当三态门使能信号OE为低电平时,三态门导通,允许Q0~Q7输出,OE为高电平时,输出悬空。当74LS373用作地址锁存器时,应使OE为低电平,此时锁存使能端C为高电平时,输出Q0~Q7 状态与输入端D1~D7状态相同;当C发生负的跳变时,输入端D0~D7 数据锁入Q0~Q7。51单片机的ALE信号可以直接与74LS373的C连接。 74ls373与单片机接口:

1D~8D为8个输入端。1Q~8Q为8个输出端。

G是数据锁存控制端;当G=1时,锁存器输出端同输入端;当G由“1”变为“0”时,数据输入锁存器中。

OE为输出允许端;当OE=“0”时,三态门打开;当OE=“1”时,三态门关闭,输出呈高阻状态。

在MCS-51单片机系统中,常采用74LS373作为地址锁存器使用,其连接方法如上图所示。其中输入端1D~8D接至单片机的P0口,输出端提供的是低8位地址,G端接至单片机的地址锁存允许信号ALE。输出允许端OE接地,表示输出三态门一直打开

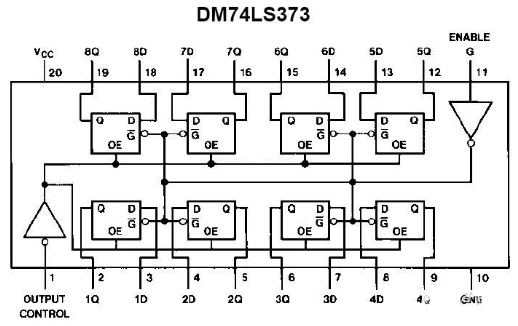

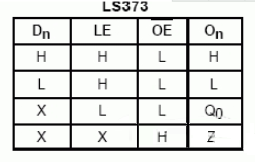

三、74ls373逻辑电路真值表

1、74LS373逻辑图

2、74ls373真值表

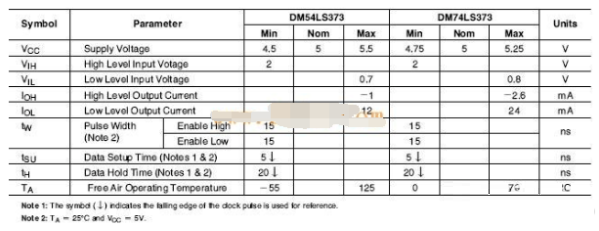

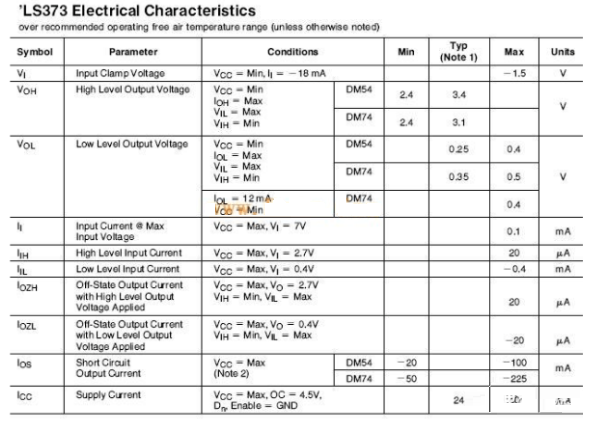

四、74ls373参数

1、74LS373电气参数

2、74ls373推荐工作条件