一、系统概述

1.设计目的

本方案的目的在于运用Cyclone器件中的逻辑单元来设计和实现(单通道)GPS接收机。该设计不仅能对地面GPS接收机作数字基带处理,也能作为测试GPS接收机的可改装平台,还可以开发成为人们了解实际GPS处理操作的学习硬件平台,同时它又足一个研究GPS接收机的试验平台,可检验基带处理和导航处理的新算法。本设计也评估了导航算法的性能。

2.应用范围

目前GPS接收机已日益广泛应用于电子类消费商品中,如新式钟表、轿车和手机。从自动导航系统、航海导航系统到飞机导航系统,GPS接收机都有着广泛的应用。如太窄中的卫星定位和轨道限定,现在已经有可能实现定位精度只有几米的差分GPS,而目.机载GPS接收机也将成为许多卫星任务中的一个组成部分。GPS接收机主要有两个应用:一个是对时间的测定,精度可达到几个毫秒;二是对移动车辆的定位和跟踪。

3.为什么使用Nios处理器

确定用户的方位需要经过复杂的计算,如求tan的反函数、求模和其他一些迭代运算。在FPGA中执行这些运算并不明智,因为它的硬件将会非常复杂,我们可以用处理器来完成这止匕操作。在大多数(3PS接收机中,专用集成电路,ASIC)已经用于基带处理,其中用一个ARM处理器来完成导航算法。但是还有一种方法能够实现单芯片GPS接收机,这就是使用(2yclone器件实现单芯片GPS接收机。由于Cyclone器件除了包含一个处理器以外,还有人量的逻辑门电路,所以我们采用了具有嵌入式Nios处理器的Cyclone器件,通过配置Nios嵌入式软核处理器来满足低成本的要求。每个Nios处理器使用最少的逻辑,为其他的系统函数留…足够的资源,而且呵以用Nios软核处理器白定义指令进行软件编码。导航算法包含一些特殊函数的逆运算,如求tan的反函数、求平方根和矩阵求逆。因此,明智之举是对所有这些特殊操作编写指令,然后在需要的时候调用它们。此外,由于C语言具有交叉编译特性,因而可以很容易完成C代码的转化。

二、功能说明

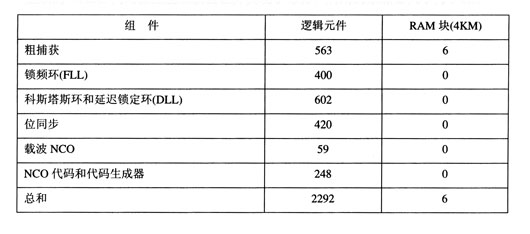

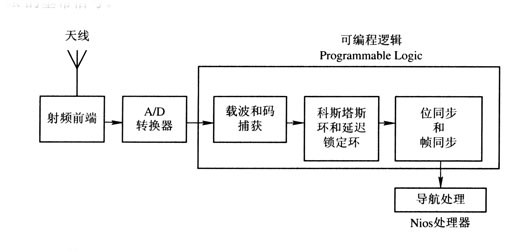

GPS信号的处理有多个步骤。在冷启动的条件下,首先要确定对于用户来说24颗GPS卫星中的哪一颗(最少有一颗)是可见的。图1示出了GPS接收机的方框图,数字基带信号是通过对中频信号进行数字化而得到的,传统的射频前端输出的中频信号(1.403MHz)被量化为2bit的基带信号。

图1 C2yclone器件中的执行块和Nios处理器中的执行块的大体框图

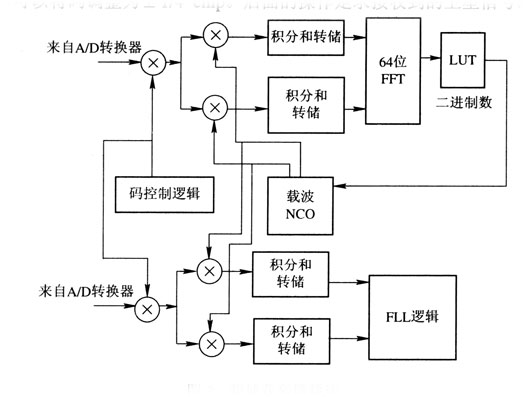

1.粗捕获

基带信号处理的第一步是粗捕获。经过这一步,不确定的载波频率从±10 kHz降到±250Hz。这一步涉及到范围在±1/4 chip内的各种码相位的调整,通过快速傅里叶变换可以估计出载波频率。在图2中,解扩(码移除)是通过将输入信号和本地码相乘实现的。用常规序列码搜寻技术可以将码调整为±l/4 chip。后面的操作是求接收到的卫星信号码与一个本地

图2粗捕扶和锁频环

Gold码的相关性,这个信号随后再与一个频率为1.403 MHz的本地载波相乘。抽取是为了减少要处理的样本数,但是抽取率是由积分和转储块输出所需要的采样率决定的,而反过来最大不确定载波频率又决定积分和转储块。在当前的情况下,最大的不确定载波频率是20kHz。根据奈奎斯特理论,积分和转储块的输出采样频率应该大于40kHz,在5.714 MHz下对120个样本执行积分运算后,输出的采样率变为47.6 kHz。由于时延是由频率分辨率决定的,所以必须注意积分和转储的输出。好的频率估计方法是通过锁频环(FLL)实现的,锁频环将频率的不确定性从±250Hz降到大约±40 Hz。FLL决定了由I信号和Q信号生成的相图旋转率。本地载波与接收信号的频率差的估计反馈到NCO(数字控制振荡器)。

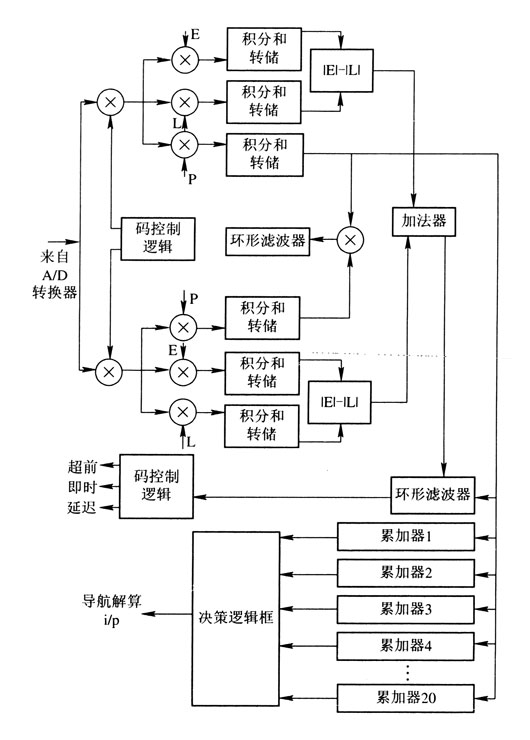

2.载波和码跟踪

在估计载波频率之后,接着要执行码相位跟踪。这一步是通过科斯塔斯环和延迟锁相环(DLL)来实现的(如图3所示)。这个框图包括产生本地载波的NCO以及超前码、延迟码和即时码的时钟。载波跟踪是通过一个二阶科斯塔斯环实现的。科斯塔斯环降低了频率差并且使

图3科斯塔斯环、DLL和同步装置

相位锁定在固有的多普勒频移上。同样,延迟锁定环用于使卫星码与本地码同步。这里用了二分之一码片间隔的二阶延迟锁定环。框图中还用到了累加器和乘法器。

我们计划用一个大的门阵列(如Cyclone器件)来处理除帧同步以外的基带信号。硬件部分由数字控制振荡器、累加器和一些组合逻辑块组成,帧同步和导航数据处理用Nios处理器实现。

三、性能参数

设计的最终目的是获得用户的位置信息,然而这要求设计中的所有组件都有合适的性能。

确定用户位置需要下面的组件都有好的性能:

射频前端。

数字基带处理。

导航数据处理。

这里我们着重于数字基带信号处理,它包括同步和解调模块。从同步的观点来看,接收机必须能够跟踪载波和码元上的中等级别多普勒,我们通过这一点来设计接收机,甚至在大约百万分之十的时钟抖动存在的情况下,也必须实现同步。这些就是设计同步模块的参数,而合适的解调是对位同步和帧同步的正确操作。

导航数据处理需要很快的速度,而且对方位的计算时间也是一个重要的参数,那是由于我们的目的是使首次定位的时间(TTFF)最短,而它又是由基带处理和导航数据处理的速度来决定的。

四、设计结构

1.硬件结构

粗捕获和锁频环的结构如图2所示,科斯塔环、DLL和位同步装置的结构如图3所示。

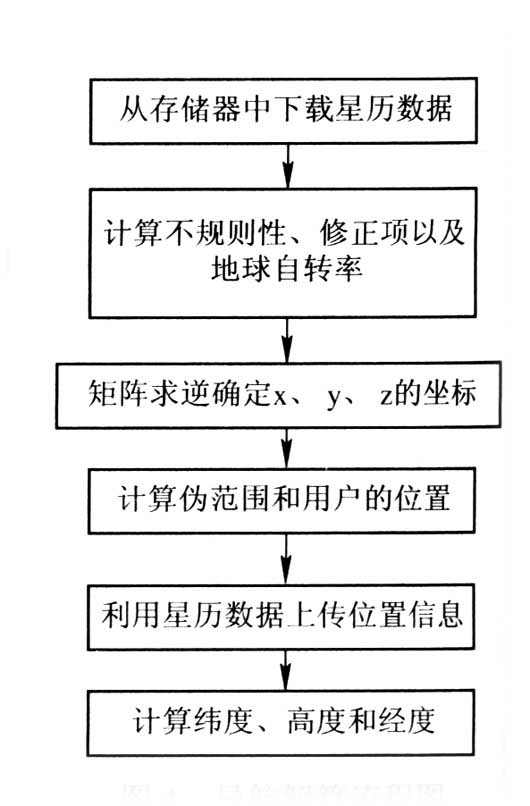

图4导航解算流程图

2.软件结构

解算流程图如图4所示。

五、实现细节

1.可编程逻辑

1)粗捕获

按照以上每一部分介绍的方案可以完成粗估计。这些组成模块如FFT、NCO和代码生成器很难用VHDL。语言编写。

具体说明如下:

(1)FFT的点数:64。

(2)NCO中用的位数:27。

(3)累加器的大小:9。

(4)Gold码产生器(移位寄存器的大小):10。

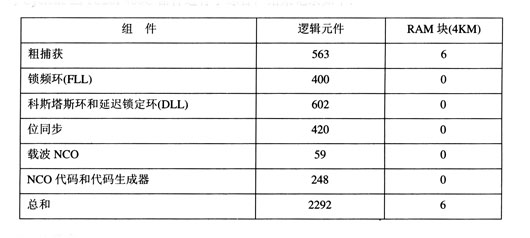

FLL中的累加器大小为19bit。我们对Cyclone EPlC20F400C器件的代码进行了仿真和综合,并通过综合前和综合后的仿真验证了它的功能。

2)载波和代码跟踪

我们为科斯塔斯环和延迟锁定环编写了VHDL语言代码。这里将累加器的大小增加到了16bit,首次通过综合前的仿真对科斯塔斯环和延迟锁定环的工作性能进行了验证。我们针对Cyclone EPlC20F400C器件进行了综合,结果记录如下:

3)位同步

生成的VHDL代码在性能上被验证并实现了综合,所用的累加器大小为5bit。

2.Nios处理器

导航算法首先是由C语言验证的,C代码可以交叉编译成Nios汇编语言。