本文采用脉冲多普勒、数字波束形成等技术,为某型雷达导引头信号项目设计了其关键部分——雷达数字信号处理机。本处理器采用FP GA平台实现,文中详细介绍了该处理器基于FPGA的基频信号产生模块、回波信号采集模块、控制信号产生模块和时钟模块等硬件模块的设计思路。

1 系统方案设计

目前,主要采用三种方法实现雷达数字信号处理系统设计:基于DSP技术实现雷达数字信号处理,基于“FPGA+DSP”技术实现和基于FPG A技术来实现。本方案选用Xilinx Virtex4 FPGA XC4VSX55,其属于Xilinx SX系列,专用于高速数字信号处理领域,FPGA非常适合于高速数据的采集控制、高速数据传输控制,且目前的主流FPGA均含有硬件乘加器、大量的逻辑单元、流水线处理技术等硬件结构,可高速完成FFT、FIR、复数乘加、卷积、三角函数以及矩阵运算等数字信号处理。高端FPGA更是含有大量的DSP单元、RAM单元、MGT高速传输单元、DDRII数据控制器等IP核,这些均是实现高速实时数字处理的重要资源。此外,FPGA编程灵活,易于升级。其高度集成性和高灵活性使对外部硬件的需要更少,额外的硬件开销大大减小,非常适用于雷达数字信号的处理和将来的算法升级。因此本方案采用FPGA技术进行雷达信号的处理。

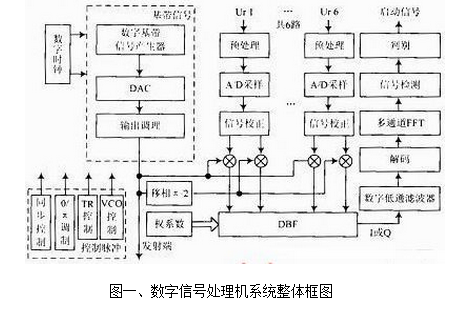

根据项目的设计需求,设计的雷达数字信号处理机系统整体框图如图1所示。

输入调理电路对接收到的回波信号进行预处理,预处理过后的信号经ADC转换为数字信号;采样后的信号经频率搬移,将100MHz的中频信号搬移到20MHz,然后对6个通道的信号进行幅度校正,消除通道间的不平衡问题。校正后的6路信号分别与两个正交本振信号相乘,进行数字混频,完成信号的正交分解,得到12路I/Q正交信号。12路I/Q信号与预先设置的权值进行加权计算并进行累加,完成数字波束形成(DBF),得到一路合成信号;通过FIR低通滤波器,对数字波束合成后的信号进行数字滤波,滤除30 MHz以上的谐波信号;由于发射信号采用了伪码调相技术,所以对DBF后的信号依照发射信号的m序列进行伪码解调(即对回波信号进行相位变换),完成回波信号的解码。对滤波后的信号进行相参累积,累积次数达到设定值后,进行FFT变换;FFT结果与检测门限进行比较,当发现回波信号特征时,给出回波的通道号和频率,并给出启动信号。

2 系统实现

2.1 硬件设计

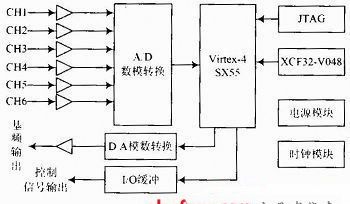

结合系统需求和系统总体设计,本系统的硬件主要包括A/D采样部分、D/A输出部分、控制信号输出部分、时钟部分、FPGA设计及配置、电源管理等六大部分,总体框图如2图所示。各功能模块介绍如下:

图二、数字信号处理机硬件框图

(1)A/D采样部分

根据性能指标,系统外接6路模拟信号,信号频率为100MHz,输入信号幅度为±1 V,幅度分辨率为0.5 mV。因此设计了两片A/D转换模块ADS6444实现带通欠采样,单片ADS6444支持4通道模/数转换,最高采样频率为105 MHz,采样位数为14 b的高性能A/D转换电路,输入信号量程为2 VPP,幅度分辨率为0.12 mV。配合前端数据调理芯片THS4513,能满足系统对采样电路的需求。

(2)D/A转换电路

无论是调频连续波或脉冲多普勒调制方式,均需要对外输出100MHz的基频信号,因此设计了D/A转换电路。D/A转换芯片采用MAX5887,它是14位、500 MSPS数模转换器(DAC),工作电压为3.3 V,提供76 dBc的无杂散动态范围(SFDR)(fout=30 MHz时)。该DAC支持500MSPS的更新速率,且功耗小于230mW。

(3)控制信号输出部分

控制信号输出TTL的信号,TTL信号采用+5 V供电,而数据处理芯片FPGA采用的为3.3 V的LVTTL电平,为实现信号的正确传输,需要信号转换,因此设计了I/O缓冲模块实现LVTTL到TTL的信号转换。I/O缓冲器使用采用美国TI公司的16位同向缓冲器SN74ALVTHl6245,可以完成LVTTL到TTL的电平转换,最高开关频率可以达到80 MHz以上,同时输出电流大,可以带动高功耗设备。

(4)时钟部分

数/模转换部分、模/数转换部分、FPGA正常工作均需要低抖、高稳定性的时钟,在此使用专用时钟芯片AD9517来产生系统需要的各个时钟。AD9517是一款集成高频时钟发生器,具有如下特点:低相位噪声、VCO频率变化范围为1.75~2.25 GHz,4路LVPECL时钟扇出,输出频率范围为50 MHz~1.6 GHz可调,4路LVDS时钟扇出,输出频率范围为25~800 MHz可调,4路LVDS时钟扇出可设置为8路CMOS时钟扇出,且相位可调、可串行控制。

(5)FPGA设计

FPGA要完成对A/D采样数据的数据处理、D/A转换的数据输出、控制信号的产生、核心算法的实现、USB调试接口的数据输入/输出等,是整个系统设计的重要部分。根据系统需求分析,使用了Xilinx Virtex4SX55。Virtex4 SX55含有512个DSP处理单元,具有强大的数据处理能力,能够满足本系统的信号处理需求。

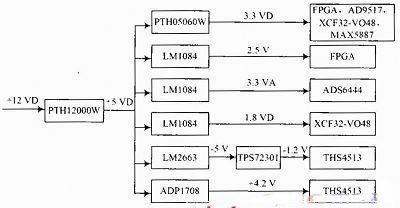

(6)电源管理

本系统采用电源管理模块将+12 V的外部电源进行稳压并分成各种幅度的电压供各个模块单独供电,满足各个模块对电压的严格需求。其电源供电系统结构如图3所示。

图三、电源系统供电结构

2.2 软件设计

本文设计的雷达数字信号处理机的软件没汁主要分为FPGA程序设计、系统驱动设计和用户软件设计三个部分。FPGA程序是系统算法的核心,完成ADC的控制以及DBF算法等;系统驱动设计和用户软件设计主要完成系统的人机交互功能,不是本文讨论的重点,此处只讨论FPGA程序的设计。

FPGA程序主要完成信号处理算法。该程序利用Xilinx公司提供的System Generator工具,对数字信号处理的过程进行建模和设计。Syst em Generator适于利用FPGA设计高性能数字信号处理系统。它利用业内最先进的FPGA开发高度并行系统提供系统建模和从Simulink与Matlab自动生成代码的功能,System Generator整合了DSP系统的RTL、嵌入式、IP、Matlab和硬件元件DSP建模。它利用包含信号处理(如FIR滤波器、FFT)、纠错(如Viterbi解码器、ReedSolomon编码器/解码器)、算法、存储器(如FIFO,RAM,ROM)及数字逻辑功能的Xilinx模块集,在Simulink内构建和调试高性能DSP系统。Xilinx模块集提供的模块可以使用户导入Matlab功能(如创建控制电路)及HDL模块,迅速完成复杂的数字信号处理算法设计。

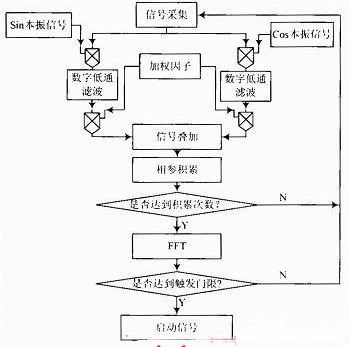

一路回波信号经A/D采集后的数字序列分别与两个正交本振信号进行相乘,完成正交变换,得到两路I/Q信号。然后,通过数字低通滤波器实现数字混频。本设计在这里选择正弦和余弦两个信号作为正交变换的本振信号,无论从数学运算上,还是具体实现上都能确保其正交性。设计中采用的是6单元均匀线阵天线,因此共得到12路I/Q信号。12路I/Q信号与加权因子相乘后进行数字波束合成,得到两路I/Q信号,然后进行信号叠加。叠加后的信号进行相参积累,当积累次数达到设置值时,进行FFT处理;否则,继续信号采集过程。将FFT处理的结果和设置的门限相比较,如超过门限时,触动启动信号;否则,继续信号采集过程。FPGA处理的流程如图4所示。

图四、FPGA信号处理流程

3 系统测试

在实际条件下,对数字信号处理机中的DBF系统合成波束的天线方向图进行了测试,以检验是否和理想条件下的天线方向网一致。具体步骤如下:

(1)测试环境:某研究所暗室。

(2)测试条件:6元15 mm接收天线成均匀直线阵排列、1元发射天线、雷达数字信号处理电路板、转台以及其他必要设备。

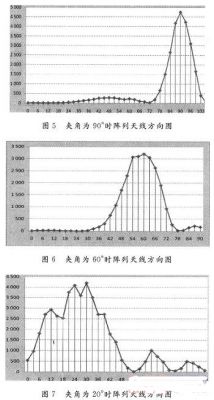

(3)测试方法:将6元接收天线放置在转台的0°刻度所在的直线上,测试的信号源放在转台前方,并在90°刻度的延长线上。此时设定阵列天线所在的直线为x轴,法线方向为y轴,转台中心为坐标零点。转动转台,使信号源与天线的夹角分别为90°,60°,20°,调整阵列天线权值,使主瓣方向指向信号源方向。调整完成后,测量并记录三种情况下的天线方向图。

(4)测试结果:根据实测数据绘制的三种情况下的阵列天线方向图如图5所示。

图五

由图可知:实测天线方向图的包络与理想条件下的天线方向图基本一致,从而验证了本设计中的数字信号处理机基本达到理想波束合成对数字电路的性能要求。但是,由于接收天线元个数较少,在信号源与阵列天线之间的夹角较小时,接收天线的增益较小,导致DBF系统无法将主瓣完全调到目标角度上。

4 结语

本文提出了一种基于FPGA的雷达数字信号处理机设计,接收机采用了脉冲多普勒、数字波束形成等主流雷达技术。本文对其硬件部分的主要模块和FPGA处理流程进行了简要介绍。暗室中测试出的接收机的方向图与理论值基本一致,说明接收机达到了系统的需求。