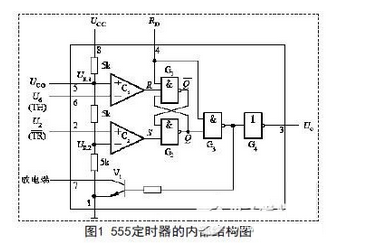

555定时器的内部结构(如图1所示):

(1)分压器

①5脚悬空时。②5脚外接控制电压时。

(2)电压比较器

电压比较器C1和C2是两个结构完全相同的理想运算放大器。比较器有两个输入端,分别用1和0表示相应输入端上所加的电压,用表示比较器的比较结果(1代表高电平,0代表低电平)。

555定时器组成的多谐振荡器

由555定时器构成的多谐振荡器如图3所示,RA,RB和C是外接定时元件,电路中将高电平触发端(6脚)和低电平触发端(2脚)并接后接到RB和C的连接处,将放电端(7脚)接到RA,RB的连接处。由于接通电源瞬间,电容C来不及充电,电容器两端电压为低电平,小于(1/3)Vcc,故高电平触发端与低电平触发端均为低电平,输出为高电平,放电管V1截止。这时,电源经RA,RB对电容C充电,使电压按指数规律上升,当上升到 (2/3)Vcc时,输出为低电平,放电管V1导通,把从(1/3)Vcc上升到(2/3)Vcc由于放电管V1导通,电容C通过电阻RB和放电管放电,电路进人第二暂稳态,其维持时间的长短与电容的放电时间有关,随着C的放电,下降,当下降到(1/3)Vcc时,输出为高电平,放电管V1截止,Vcc再次对电容C充电,电路又翻转到第一暂稳态。

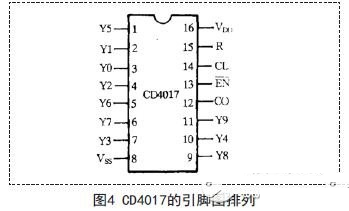

CD4017逻辑功能

CD4017芯片是十进制计数器/时序译码器,应用极其广泛。图4是CD4017的引脚图排列,采用16脚双列直插式塑料封装形式。CD4017的CL端在输入时钟脉冲的上升沿计数,时钟允许端EN为“0”时,允许时钟脉冲输入,为“1”时就禁止时钟脉冲输入。在输入时钟脉冲的作用下,10个译码输出Y0~Y9依次为高电平。R为复位端,当R=1时,计数器清零,Y0为“1”,其余Y1~Y9均为“0”.CO为进位输出端,CD4017记满10个数后,CO端输出一个正的进位脉冲。

电路实现

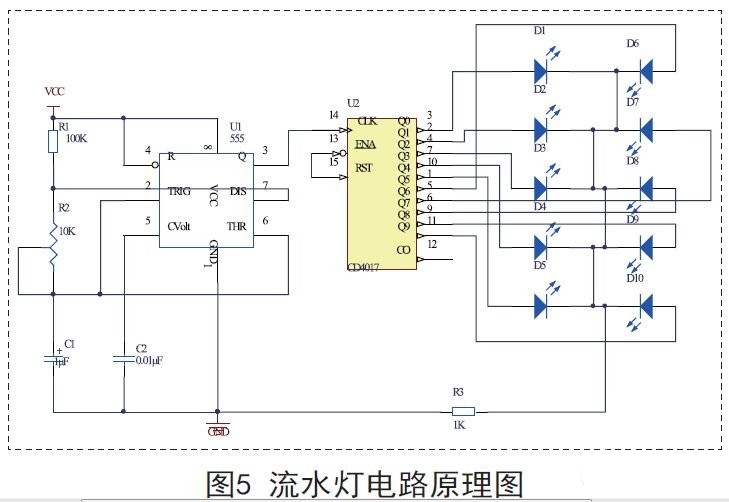

流水灯电路原理图(如图5所示):

流水灯电路原理

该电路由时基集成电路NE555构成的多谐振荡器和CD4017十进制计数/译码电路组成。电源接通后,经R1、R2给电容C1充电,使逐渐升高,当时,3脚(Q端)输出为高电平。当上升到超过时,3脚输出仍为高电平。当继续上升到略超过时,RS触发器状态发生翻转,3脚输出为低电平,同时 C1经R2及7脚内导通的放电管VT到地放电,迅速下降。当下降到略低于时,触发器状态又翻转,3脚输出变为高电平。同时,7脚内导通的放电管VT截止,电容C1再次进行充电,其电位再次上升,一直循环下去。根据,可以看出,通过改变电位器R2的电阻值的大小,即可以改变振荡器的振荡周期,从而改变3脚输出高低电平的转换时间,进而改变流水灯的速度。对于CD4017,其14脚接收来自555定时器3脚的输出脉冲。当555定时器的3脚的输出电平状态发生翻转时,14脚接收到高低电平的变化,触发十个输出引脚交替输出高电平,点亮相应引脚的LED灯。随着时间的进行,十个LED灯相继被点亮,形成流水灯。

555定时器是一种模拟和数字功能相结合的集成器件,通过外围元件的简单组合,可以组成许多基本实用的电路,最基本且应用最多的有单稳态触发器,施密特触发器,多谐振荡器三种。以这些基本电路为基础,又可以和其他组合形成各种各样实用的电子电路,实现各种各样的功能,如定时器、分频器、脉冲信号发生器、玩具游戏机电路、音响告警电路、自动控制电路、电源交换电路、频率变换电路元件参数和电路检测电路等。相信在不久的将来,555定时器将应用在更多领域,为我们的生活增加更多新鲜的元素,并使我们的生活更加丰富多彩。