引言

随着产业技术的不断发展,对单片机控制的要求也越来越高,需要单片机具备更高的反应速度和更强的数据处理能力,各种高性能的新型单片机得到了迅猛的发展和应用。单片机上主要是高速的数字信号,弱信号很轻易受到外界的电磁干扰,同时,单片机系统也会发生掉电、死循环等题目。在产业控制场合,一旦控制发生错误,将会造成无法计算的损失。因此,如何进步控制的可靠性是长期以来的一个重要题目。本文介绍了应用32位高性能单片机MC68HC376的一种实际开发方案,同时重点讨论了进步系统可靠性的设计和实现方法。

MC68HC376是Motorola公司推出的一种新型的32位高性能单片机,具有极强的数据处理、逻辑运算和信息存储能力,且支持BDM(Background Debug Mode)模式。通过简易的专用电缆接口,可以直接对微控制器系统进行仿真开发和烧录程序。此外,由于MC68HC376内部集成度高,外部扩展工作少,因此本身具有较强的抗干扰能力;同时通过外部硬件电路以及软件的抗干扰设计,控制系统可以实现较高的可靠性。

1 控制系统的基本结构设计

MC68HC376的集成度高,其主要功能模块包括32位CPU;系统集成模块(SIM);4K备用RAM;8K片内ROM;10位队列式的模数转换器(QADC);队列式串行通讯模块(QSM);可构造时钟模块(CTM4);时间处理单元(TPU);

3.5K静态TPURAM;CAN控制模块(TOUCAN)。其基本性能如下:

(1) 24位地址总线、16位数据总线结构,支持32位数据操纵。

(2) 2个8位双功能I/O,1个7位双功能I/O,16~44个模拟量输进通道。

(3) 具有系统保护逻辑,同时可进行时钟监视和总线监视。

(4) 速度快,在4.194MHz的晶振下系统时钟可达20.97MHz。

(5) 功耗低,具备低功率休眠功能。

(6) 支持高级语言和背景调试。

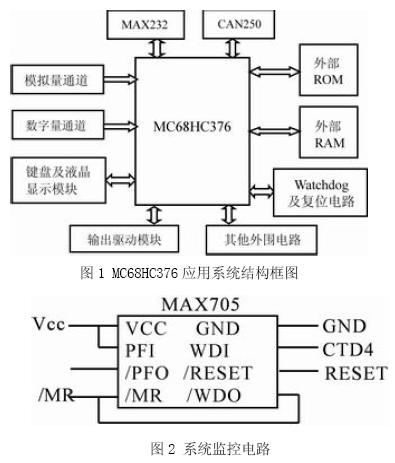

系统扩展的基本结构 MC68HC376 内部集成度较高,因而其所需的外围扩展工作较少。基本结构包括外部Flash ROM、RAM、模拟量输进通道、数字量输进通道、键盘、液晶显示、RS-232电平转换器MAX232和CAN控制器CAN250等,其结构框图如图1所示。本文重点讨论系统的可靠性设计。

2 系统的可靠性设计

2.1 微处理器硬件监控电路

本文采用监控器MAX705芯片构成外部监控电路,电路外部接线如图2所示。该电路具有看门狗定时器、自动和手动复位功能,以及电压门限监测功能。

由于在系统上电、掉电以及供电电压不足时, CPU 和总线逻辑状态不确定,因此应该将微控制器维持在复位的状态,以避免控制错误。对于MAX705,复位门限电压为4.65V,故当Vcc低于4.65V时,系统保持在复位状态。同时,将Vcc与PFI引脚相连,当Vcc低于1.25V时,由PFO引脚输出示警信号,若较长时间处于电源示警状态,则可能出现电源故障,应该加以处理。

当系统正常运行时,由MC68HC376的CTM4模块的CTD4通道以小于1.6s的间隔定时向MAX705的WDI引脚提供脉冲;一旦系统不能正常运行而导致MAX705的WDI引脚失往脉冲时,看门狗定时溢出使得/WDO为低,由于/WDO与手动复位引脚/MR相连,因此/RESET脚向MC68HC376发出低有效的复位信号,使系统恢复到复位状态。

2.2 外部滤波电路

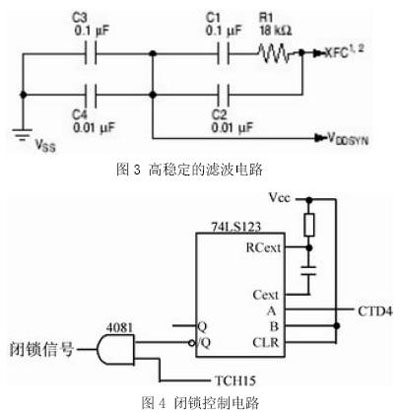

由于系统采用外部参考频率源,为了进步系统频率的稳定性和可靠性,所以需要在MC68HC376的XFC脚上接进滤波电路。该电路应尽可能降低XFC脚的泄露电流,以进步时钟的稳定性和内部锁相环的性能。图3所示为高稳定的滤波电路。

2.3输出驱动电路可靠性设计

控制装置通过对系统状况进行监测和分析后,向控制和调节的动作单元提供控制信号。假如输出信号受到干扰或者由于装置故障而发出错误的控制信号,那么会因产生错误的调节控制动作而使系统受到危害。因此,对于输出驱动电路应该加以相应的闭锁控制和抗干扰设计,以进步控制的可靠性。

(1) 闭锁控制电路

这里采用可再触发双/单稳态多谐振荡器74LS123 来构成输出闭锁电路,电路接线如图4 所示。 将74LS123的A脚与MC68HC376的CTM4模块的CTD4通道相连,由于在正常情况下CTD4定时提供脉冲,使得振荡电路不能发生翻转,此时,/Q保持为1;假如装置故障,使得CTD4失往脉冲,则振荡电路使得/Q翻转变为0,因此闭锁信号变为0对输出控制信号闭锁。

同时,与门4081的另一脚接至MC68HC376的TPU模块的TCH15脚,直接由MC68HC376控制。在正常运行中,当需要输出控制信号时,置TCH15为1;当不需要输出控制信号时,置TCH15为0,则使闭锁信号为0,闭锁输出部分,这样就防止了由于干扰或其他原因造成的误动作。

(2) 控制信号输出部分的抗干扰设计

当闭锁信号开通时,输出控制信号可能由于扰动而出现偏差,因此应设计相应的输出电路形式来减小扰动的影响。输出电路的形式如图5所示(这里只画出一路输出信号)。

采用单线控制时,一旦受到干扰就会使控制信号的电平发生变化,从而造成误动。这里采用“0,1”控制方式,用两根邻近的控制线,一根直接接至与门4081,另一根经过非门4069接至4081,即当两根控制线为“0,1”时输出有效的电平信号1。这样,当存在高扰动或低扰动使得控制线同时变为1或0时,输出无效的电平信号0。本系统中,以CTM4模块的CPWM7引脚和闭锁信号一起控制开启信号;开启信号与MC68HC376的控制信号一起控制动作输出信号。这样就充分进步了输出控制的可靠性。留意,单片机的I/O控制信号应使用上拉电阻。

2.4 掉电报警电路

当系统的某一级工作电源掉电时,控制装置将不能正常运作,或者控制信号得不到正确执行。这时应该发出报警信号,掉电报警电路如图6所示。将各等级的工作电源通过关隔MOC8050串接起来,一旦发生掉电的情况,掉电报警处的电平由高变为低,启动报警装置。软件可靠性设计

2.5 软件看门狗

在MC68HC376的SIM模块中,有一个软件看门狗,在监控程序中,可以开启软件看门狗,配合进步系统的可靠性。该软件看门狗由MC68HC376的系统保护控制寄存器(SYPCR)中的SWE位控制开启。当SWE位为1时,看门狗启动,开始计时。在装置正常工作时,程序应该在软件看门狗溢出之前对软件服务寄存器(SWSR)先后写进55H和AAH,当写进完成之后,软件看门狗就会清除当前计时值,重新开始计时。

假如计时值溢出,则会使MC68HC376的/RESET引脚有效,系统复位。这样,就可以在程序死循环或者由于其它原因而导致程序跳飞时自动回复到复位状态。

看门狗的溢出时间由系统频率以及SYPCR寄存器的看门狗分频位(SWP)和看门狗定时区(SWT[1:0])决定,如表1所示。选择看门狗溢出时间时应该留意大小适中,若取值过大,则程序可能会较长时间处于死循环或跳飞状态,从而导致控制错误或失效;若取值过小,则会增加程序负担,降低装置运行效率。

2.6 程序的区域划分和操纵级别控制

CPU32可进行两种优先级别的操纵:监控级别和用户级别。在监控级别下,CPU可以对所有的内部集成资源和所有的指令进行操纵,而在用户级别下,它对一些寄存器和指令的访问会受到限制。在程序中有效地利用这种优先级别会使内部资源和一些系统指令得到有控制的访问,从而进步系统运行的可靠性。CPU32的状态寄存器SR中的S位决定CPU的工作级别,当S=1时CPU处于监控级别;S=0时CPU处于用户级别。

一般情况下,单片机的程序区和数据区在同一个物理地址空间。对于MC68HC376,可以通过功能码FC[2:0]来扩展和划分外部物理空间,对FC[2:0]实现外部解码,可以使监控级程序、监控级数据、用户级程序、用户级数据分别使用各自独立的地址空间。对于MC68HC376内部的各个模块,可以通过其相应的结构寄存器中的SUPV位来确定该部分的通用寄存器所处的地址空间,当SUPV=1时,将相关的寄存器放置于监控级数据地址空间,CPU只有在监控级别时才可对其访问和操纵;当SUPV=0时,将相关的寄存器放置于数据级数据地址空间,CPU可任意对其进行访问和操纵。这样,整个程序结构性强,按级别控制访问,增强了运行的可靠性。

2.7 总线监视器

MC68HC376进行内部总线操纵时,数据选通应答引脚(/DSACK)和自动向量引脚(/AVEC)应该有相应的应答信号。SIM模块中的总线监视器能对/DSACK和/AVEC信号进行监视,当响应时间超过定时值就使总线错误(/BERR)引脚有效。程序应对/BERR的状态进行监视,以便及时对总线错误做出相应的处理。

总线监视器的定时值由系统保护控制寄存器(SYPCR)中的总线监视时间区(BMT[1:0])决定。BMT[1:0]=00时,定时值为64个系统时钟;BMT[1:0]=01时,定时值为32个系统时钟;BMT[1:0]=10时,定时值为16个系统时钟;BMT[1:0]=11时,定时值为8个系统时钟。程序员应根据实际的运行情况进行选择。

其它 其它一些进步可靠性的措施还包括有配置往耦电容;系统时钟电路采用独立电源VDDSYN供电,减少对MCU的干扰,而且MCU 停电时系统时钟仍可维持运行。布线时,时钟电路设置在电路板的中心;Standby RAM采用两个电源VDD和VSTBY供电,正常运行时VDD供电,发生掉电时,使其自动切换到VSTBY供电。同时,在软件中,将堆栈及一些重要数据存放在Standby RAM 有利于重要运行参数的保存。

3结语

该方案采用高性能、集成度高、可靠性强的32位新型微控制器MC68HC376为核心,同时在硬件、软件以及制板布线等方面采用多种进步系统可靠性的设计措施。应用该方案的数字式低频低压控制装置RSA800,已通过电力产业部电力设备及仪表质量检验测试中心的产品型式试验。