1 、引言

LED 显示屏应用十分广泛,是信息传播的有效工具。在某井下矿采设备监测系统中选用了ARMS3C44B0X32 位单片机作为CPU,根据应用要求,监测系统的显示部分使用16 行的单色L ED 显示屏实时显示监测数据。由于系统外设较多,端口资源十分紧张,针对这种情况开发了一种四线驱动的显示屏电路设计方案,很好地解决了这个问题。

2、 常见的驱动电路设计及改进

在常见的显示驱动电路设计中,列控制一般采用串入并带锁存的移位寄存器如74HC595 ,将数据打入锁存器中,使寄存器各引脚呈现与锁存器相同的状态来选中需要点亮的列。行控制一般采用译码器电路如4/ 16 译码器74HC154 ,控制信号经译码后选中需要点亮的行。这种硬件结构设计需要较多的控制信号线,占用单片机较多端口从而造成端口资源的浪费。

在改进的L ED 显示屏驱动电路设计方案中,行、列控制均采用串入并出带锁存的移位寄存器,控制信号的产生均由S3C44B0X的I/ O 口发送串行数据来实现,这样仅需要4 根信号线L ED 显示屏就能正常工作。

3 、显示驱动电路设计

3. 1 电路结构

LED显示屏由多个LED点阵模块构成。显示电路采用1/ 16 扫描方式,显示点阵的一行对应一路行选通信号,各行的同一列共用一个列选通信号。

当需要在L ED 显示屏上显示图文内容时,只要在行、列显示数据控制下让显示屏上相应的发光器件点亮就可以了,一次点亮一行,依次点亮各行,只要速度足够快就会产生连续的视觉感受。

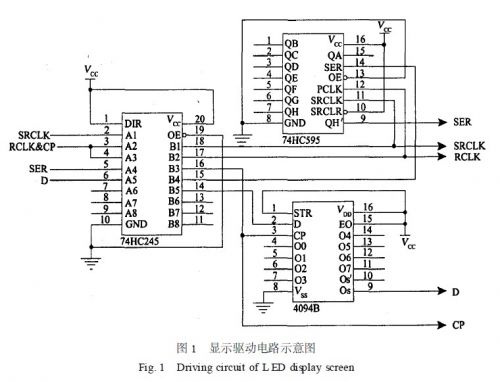

行驱动电路采用HEF4094 带锁存功能的串入并出移位寄存器。如图1 ,引脚D 为串行数据输入端,引脚CP 为移位时钟脉冲输入端,STR 为输出锁存器打入信号输入端,OE 为输出使能信号输入端,当其为高时锁存器的输出才开放,芯片输出端为00~07 ,OS、OS′作为级联输出,见参考文献。

列驱动电路采用74HC595 带锁存功能的串入并出移位寄存器。如图1 ,引脚SER 为串行数据输入端,引脚SRCL K 为移位时钟脉冲输入端,引脚RCL K 为输出锁存器打入信号输入端, EO为输出使能信号输入端,只有当其为低时锁存器的输出才开放,引脚SRCLR 为移位寄存器的清零输入端,当其为低时移位寄存器的输出全部为零,芯片输出端为QA~QH ,QH′作为级联输出,见参考文献。

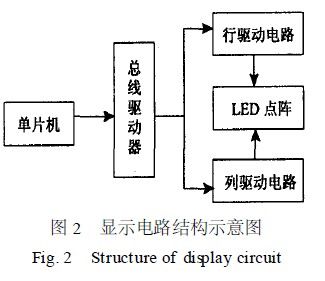

由I/ O 口送出的控制信号经总线驱动器74HC245 分别接到行、列驱动电路上。显示电路结构如图2 所示。

该L ED 显示屏为16 行×64 列点阵,共需两片HEF4094 级联以及8 片74HC595 级联。

由HEF4094 组成的行驱动器如图1 所示。

由两片HEF4094 组成16 行的驱动,图中只画出第一片。第一片HEF4094 的D 端连接I/ O 口输出的串行行显示数据,OS 端连接下一片的D 端。

两片相应的CP 并联,作为统一的串行数据移位信号。在各控制信号输入端中, STR 端(高电平有效) 、EO(高电平有效) 锁存输出使能端接直流电源正极。

由74HC595 组成的列驱动器如图1 所示。

由8 片74HC595 组成64 列的驱动,图中只画出第一片。第一片595 的SER 端连接I/ O 口输出的串行列显示数据,Q’H 端连接下一片的SER 端,各片均采用相同的方法组成8 片的级联,各片相应的SRCL K, SRCLR , RCL K 分别并联,作为统一的串行数据移位信号和输出锁存打入信号。在各控制信号输入端中,SRCLR(低电平有效) 移位寄存器清零输入端接电源正极、OE(低电平有效)锁存输出使能端直接接地。

图1 中黑箭头所指即为下一片74HC595 或HEF4904 的信号输入端。

由于行驱动电路同时驱动64 列的L ED 发光器件,按每一L ED 器件电流20 mA 计算,64 个L ED 同时发光时就需要64 ×20 = 1 280 mA 的驱动电流。因此需要用功率管驱动, 如TP122等。

3. 2 基本显示原理

采用这种显示驱动电路设计,只需4 个I/ O口分别发送SRCL K、RCL K&CP、SER、D 信号就能实现正常的显示功能,其中74HC595 的RCL K和HEF4094 的CP 共用一根信号线,由同一I/ O口发出控制信号。74HC595的SRCLR 信号输入端接直流电源正极避免进行清零操作,OE 信号输入端接地使得一旦列显示数据出现在锁存器的同时各输出引脚即呈现出相应的高低电平状态。

HEF4094的STR信号输入端接直流电源正极使得行显示数据出现在片内移位寄存器的同时即被打入锁存器从而避免锁存打入操作,OE 信号输入端接直流电源正极使得一旦行显示数据出现在锁存器的同时各输出引脚即呈现出相应的高低电平状态。因此,需要点亮某一行时,需要执行以下几个步骤:

(1) 将15 位行显示数据通过D、CP 信号依次送入到两片级联的HEF4094 中,最后一次移位在第三步完成。

(2) 将64 位列显示数据通过SER、SRCL K信号依次送入到8 片级联的74HC595 中。

(3) 发出列显示的锁存打入信号RCL K,把列显数据打到各595 的输出引脚上,完成列显示的准备工作,同时由于行移位信号CP与RCLK共用一根信号线,行显示数据完成最后一次移位,完成行显示准备工作。

(4) 行列数据都准备完毕,显示屏中被选中的那一行被点亮。

(5) 延时几毫秒保证每一行有充分的点亮时间然后进行下一行的显示。

按照以上步骤依次点亮16 行,即可让L ED屏显示需要的图文内容。

4 、LED 显示屏的软件设计

HEF4094和74HC595 都是串入并出移位寄存器,显然应用串行口驱动,但是S3C44B0X 的串口资源有限,还要用来与上位机进行通信;因此采用将并行的I/ O 口模拟成串行口的方法来解决。

这样仅需要4 个并行I/ O 口就可以完成显示任务,在程序中使用PORTD0 到PORTD3 这4 个I/ O 口,PORTD 由8 个I/ O 端口组成。

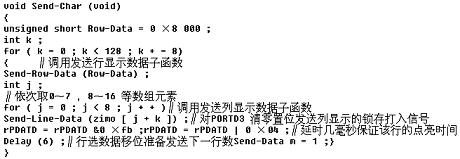

下面是已经在Hitool ForARM编译环境中通过的在16 行×64 列点阵L ED 显示屏上显示4个汉字的程序,该程序用C 语言编写,稍做修改就可以用于各种单片机系统。

首先将要显示的4 个16 ×16 点阵的汉字字模存储在数组zimo[128 ]中。

主程序代码如下:

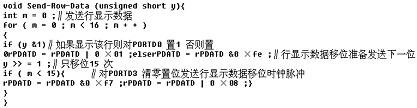

行显示数据发送子程序代码如下:

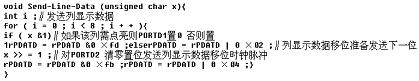

列显示数据发送子程序代码如下:

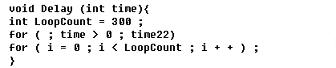

延时子程序代码如下,LoopCount 的数值可根据所选用的单片机时钟频率来设定。

5、结束语

这种设计方案大大节省了单片机的端口资源,有效简化了显示屏的电路结构,提高了整个显示系统的可靠性,根据这个设计原理可设计出各种规模的LED显示屏。