该频率计的测频范围0Hz~999Hz,测量的电压范围为0~7mV,本电路结构简单,成本低廉,对于提高动手能力加强对理论知识的灵活运用具有很大的帮助。该电路大致可分为模拟和数字两个部分:

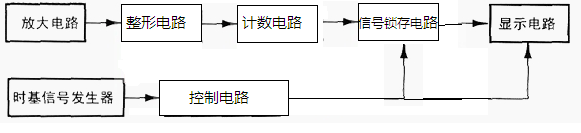

模拟部分包括信号放大电路、信号整形电路;数字部分包括计数电路、显示电路、时基信号发生电路与计数器与锁存器控制电路等,基本框如下图所示。

该 电路的整体思路就是将交变的模拟信号转换为数字信号,然后实现频率的计算。当在该电路的输入端输入微小变化的模拟信号时。经过第一部分的放大电路放大后。 再通过由比较器组成的整形电路进行整形。此时该部分输出的信号就变成了规则的数字脉冲信号,最后通过数字电路来实现计数功能。整形过后数字信号就可以通过 计数器等数字电路来处理。计数器与显示电路相连。即可显示所测的频率。其中时基信号发生电路的作用是产生一秒钟脉宽的时基信号,来控制计数器实现一秒钟的 计数,同时时基信号还控制锁存电路,当计数结束后及时锁存数据以实现稳定的显示。

二、电路原理

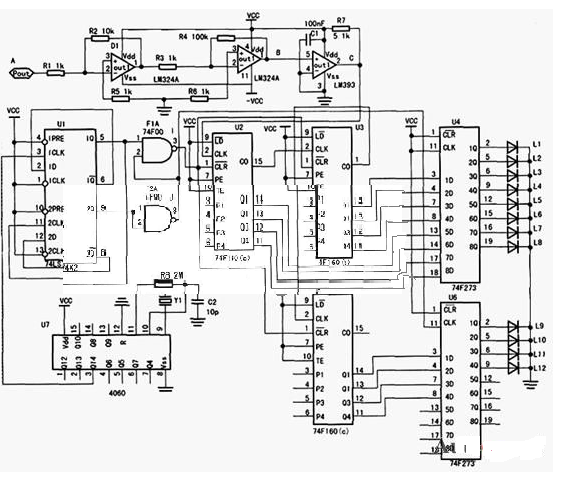

系统电路如下图所示。

(1) 放大电路:放大电路部分主要由一块LM324集成运放及外围元件组成。本放大电路采用两级放大,第一级信号的增益为20dB,第二级的信号增益为 40dB,两级的放大倍数为1000倍,其频率的带宽为0~5kHz。采用多级放大可以提高的放大电路的通频带,如果被测的信号频率较高。可以采用多级放 大来提高通频带,根据实际情况而定,由于本电路的测频范围低,对通频带不做太多的要求。图2中,A端为被测信号的输入端。B端为放大电路的输出端,接整形 电路的输入。

(2)整形电路:整形电路的主要作用是将第一部分放大的交变信号整形为数字信号(即幅度为5V的方波信号),其电路主要由比较器组成,该电路中我们选用LM393比较器,B端为整形电路输入端,C为整形电路的输出端接E端。

(3)计数电路:计数电路部分我们选用3片十进制加法计数器74LS160的级联来实现0-999Hz的频率显示,74LS160为可预置的十进制同步计数器,利用其级联,可以构成任意进制的计数器。

74LS160(a) 的2脚为脉冲信号的输入端,1脚清零端。74LS160(a)的CO进位端接74LSl60(b)的CLK脉;中输入端,74LS160(b)的进位端接 74LS160(c)的CLK脉冲输入端,三块计数器的PE、TE及LD端接电源.使计数器工作在计数的状态,CLR端接时基电路,由时基电路来控制计数 与清零。

(4)显示电路:显示电路部分主要由二块74LS273锁存器和12个红色发光二极管组成,74LS273是8位数据/地址锁存器。他是 一种带清除功能的8D触发器,主要实现对计数电路的输出信号进行锁存,由于计数器的频率较快。采用的是动态显示,我们为了显示的稳定,便于观察,所以在计 数器的输出端进行锁存。该锁存器的锁存信号由时基电路来提供,且当1脚为高电平时,11(CLK)脚是锁存控制端,并且是上升沿触发锁存,当11脚有一个 上升沿,立即锁存输入脚3、4、7、8、13、14、17、18的数据,并且立即呈现在输出脚2(Q0)、5(Q1)、6(Q2)、9(Q3)、 12(Q4)、15(Q5)、16(Q6)、19(Q7)上。74LS273的CLR端接高电平,使其工作在不清零状态。

(5)时基信号产生电 路:该电路的主要作用是产生O.5Hz的时基信号(即周期为2秒,脉宽为1秒的闸门信号)为锁存器提供锁存信号和为计数电路提供计数闸门信号,实现频率计 数与显示。时基信号产生电路由一个频率为3.2768MHz的晶振和一块CD4060分频器以及外围元件够成。CD4060(IC)是一种带有振荡器的 14级分频器电路。用作振荡器时需外接R、C元件或石英晶体和电容器。内部包含两个非门和14级2分频电路,它所产生的信号频率为32768Hz,经14 级两二分频后,得到一个2Hz的脉冲信号。下图H端为2Hz信号的输出端。

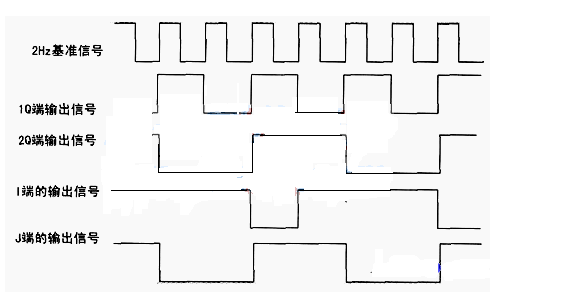

(6)计数器与锁存器控制电路该部分电路主要是控制计数电路的清零、计数与锁存电路的锁存显示。该电路的核心器件是一块 D触发器74L.S74与一块与非门74LS00组成。H为2Hz方波信号(即周期为0.5s,时基电路产生)的输入端I、J为控制信号的输出端,分别接 计数器的清零端与锁存电路的CLK时钟端,H、I、J端的信号时序如下图所示。

基准信号经过D触发器分频后便获得1Q和2Q的方波信号,经由两个与非即可得到l端和J端的方波信号。当l端的信号在高电平时计数器工作在计数状态,低电平时对计数器清零。当l端的信号处于下降沿的时候,此时J端的信号处于上升沿。

该上升沿信号使锁存器开始工作,直到下一个上升沿的到来.这样便实现输入信号的计数与锁存。

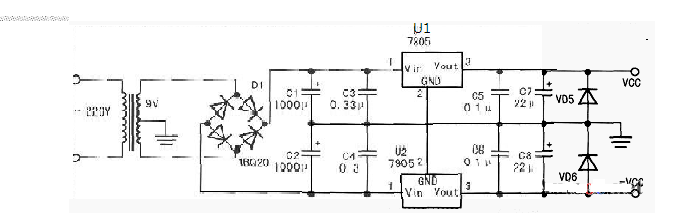

(7)电源电路:该电路的整体供电需要双5V,因此我们可以设计一个简单的双电源供电电路。电路原理图如下图所示。

三、心得体会

电路简单易懂,而且元件易选易采。该电路主要涉及到数字电子技术与模拟电子技术两本书中放大器以及计数器等许多专业知 识,通过本电路的设计与搭建,能够在提高动手能力的同时,也能够将书本所学的知识真正的应用到实践的过程中,达到理论与实践相结合的效果。感兴趣的读者不 防亲手实践一番。