1.引言

在电机驱动、UPS等系统中电压的稳定尤为重要,欠压、过压保护是必不可少的,因此通过在芯片内部集成过压、欠压保护电路来提高电源的可靠性和安全性。对功率集成电路,为提高电路的可靠性,保护电路同样必不可少。保护电路的设计要简单、实用,本文设计了一种CMOS 工艺下的欠压保护电路,此电路结构简单,工艺实现容易,可用做高压或功率集成电路等的电源保护电路。

2.工作原理分析

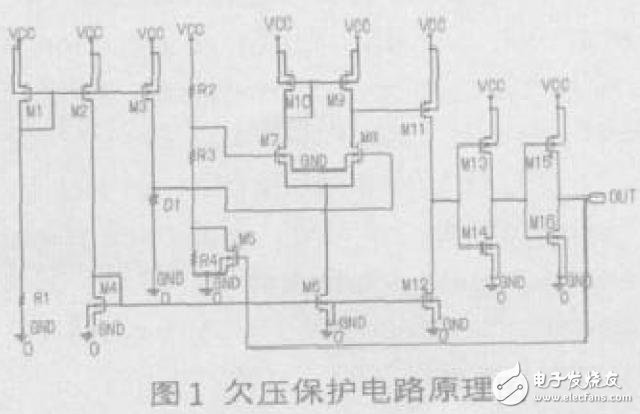

欠压保护的电路原理图如图1 所示。共由五部分组成:偏置电路、基准电压产生、欠压检测输入、比较器、反馈回路。

本电路的电源电压是15V,M1、M2、M4、R1 是电路的偏置部分,给后级电路提供偏置,电阻R1 决定了电路的工作点,M1、M2、M4 是电流镜;M3、D1产生基准电压,输入比较器的同相端;分压电阻R2、R3、R4是欠压检测输入,输入比较器的反相端;R4、M5是欠压信号的反馈回路;其余M6~M16 组成四级放大比较器。

M3、D1 产生基准电压,输入比较器的同相端,固定不变是11V,当电源电压正常工作时,反相端的欠压检测输给比较器的反相端的电压大于11V,比较器输出为低,M5截止,反馈电路不起作用;当欠压发生时,分压电阻R2、R3、R4 反映比较敏感,当电阻分压后输给反相端的电压小于11V,比较器的输出电压为高,此信号将M5 开启,使得R4两端的电压变为M5两端的饱和电压,趋近于0V,从而进一步拉低了R2、R3 分压后得输出电压,形成了欠压的正反馈。输出为高,欠压锁定,起到了保护作用。

3.参数计算

对于MOS模拟集成电路,各MOS管的工作状态和管子尺寸及宽长比决定了电路的功能和性能,下面结合0.6μm工艺,对电路的电阻及各管宽长比进行估算。设定电路的总功耗Pm《3mW,VCC是15V,将Uth近似为1V。根据总功耗可得总电流:

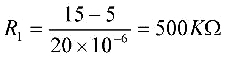

电路共有八条回路(200/8),可大致分配各路电流20 μ A 左右:故偏置电流20 μ A,即:电阻R1 的阻值大致约;

电路中MOS 管均工作在饱和区,MOS 管的饱和区的公式:

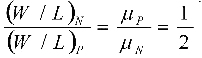

可以估算出M1 的宽长比,进而由电流镜和PMOS 、NMOS的宽长比与迁移率的关系

可得M2、M3、M4 的比值,即:

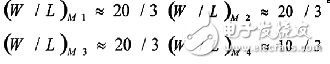

稳压管的电压值的设定要考虑工艺的实现并且要满足M3 工作在饱和区的条件下选定,这里电压值选为11V;而电阻的设计要考虑面积因素。电阻R2、R3、R4 构成分压器,设定此路中电流是30 μ A,忽略M5 的电阻,可得

其中,R3=300KΩ,R4=70KΩ

比较器的增益要足够的大,设定比较器的开环增益在80dB(104 倍)以上,由于实际制作出的产品往往比理论计算出的放大倍数小很多。因此,我们分配各级的放大倍数分别: Aμ1=50,Aμ2=20,Aμ3=10.总共的放大倍数为各级放大倍数的乘积,即为:

分配各级电流的四路总和不超过110μA(200μA-20×3μA-30μA)。故分配各级电流分别为30 μ A、20 μA、30 μA 和30 μA。这样,我们就可以根据放大倍数和偏置电流来计算出各个管子的宽长比。

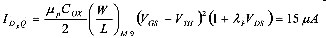

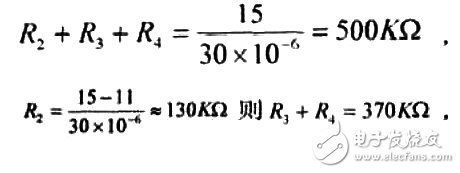

对于差分放大级。放大倍数Aμ1=50, 偏置电流为30μA,则两个支路的电流为1 5 μ A 。根据计算公式:

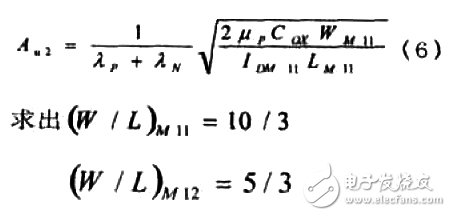

第二级,共源放大级。放大倍数A μ2=20,流过的电流为20 μ A,根据

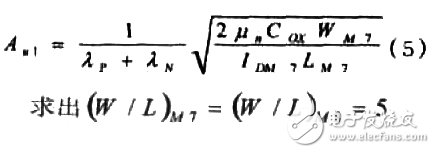

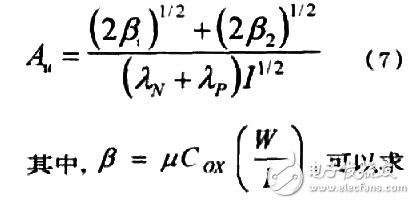

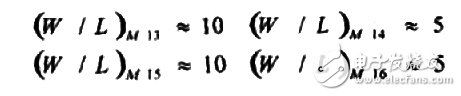

第三级和第四级推挽CMOS 放大级,由公式:

出M13~M15 各管的宽长比为:

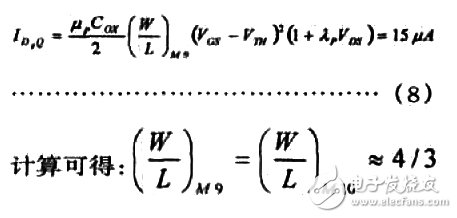

差分对的有源负载管宽长比的计算。从电压角度出发,为了保证所有的管子在信号范围内都工作在恒流区或临界恒流区,而不进入深度线性区,根据总电源电压VDD =15V,我们可以大致分配M9、M10 的静态。则:

计算可得:

4.模拟仿真结果分析

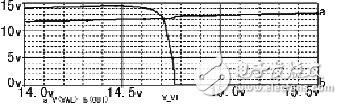

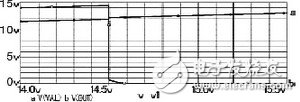

通过上面的计算所得, 利用pspice 对电路进行模拟,在模拟仿真过程中,各管的尺寸有调整,在仿真时,分别增大和减小电源电压来进行电源扫描,波形见图2。 从仿真的波形中可以看出:当增大电源电压时,电压低于14.78V时,欠压锁定;当减小电源电压时,电压低于14.5V 时,欠压锁定。仍可进一步调整参数,来改善增大电源电压时的欠压曲线。

(a)电源扫描的波形(增大电源电压)

(b)电源扫描的波形(减小电源电压)

图2电源扫描的波形图

5.结论

此欠压保护电路结构简单,工艺易实现,可用于功率ic 稳压电源保护中,当采用不同的工艺时,计算参数的方法相同,也可以采用等比例缩小的原则确定参数。对于一般的欠压保护,本电路已经足够。如果对欠压保护精度和灵敏度要求很高的电路,则可在此电路的基础上将稳压输入部分换成稳压源,将比较器选用精度更高的比较器,但这样结构复杂,功耗大,成本高。