摘录 自《玩转IP core》

第一:系统内大部分器件的动作都是在时钟的跳变沿上进行,这就要求时钟信号时延差要非常小,否则就可能造成时序逻辑状态出错。

第二:时钟信号通常是系统中频率最高的信号。

第三:时钟信号通常是负载最重的信号, 所以要合理分配负载。

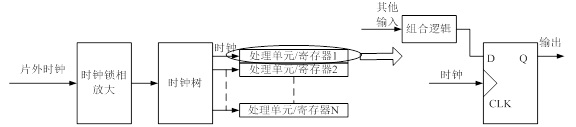

全局时钟(Global Clock)。它是由片上的时钟管脚引入,经过锁相和放大之后,输出给寄存器的稳定、可靠的信号。这种时钟的时延被设计的最小,相对时延也最小。

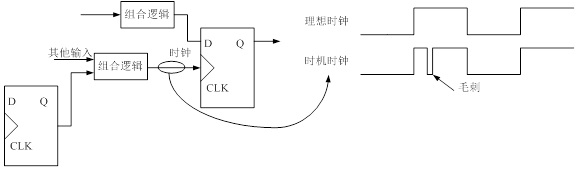

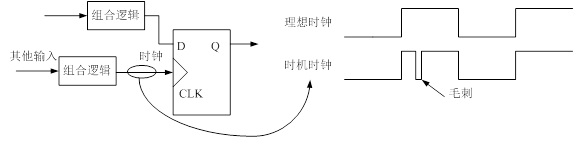

门控时钟。这种时钟从一些信号经过组合逻辑产生.

多级逻辑时钟。它不仅仅用了组合逻辑还加入了前级寄存器的输出。所以毛刺也无极限啊。

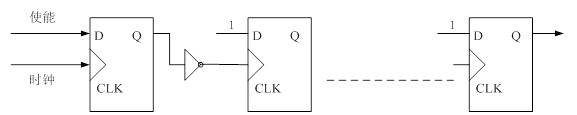

行波时钟。上级寄存器的输出作为下级寄存器的时钟逐次传下去。理论上,行波时钟可以非常完美的运行下去。但是,在这里总是有但是的,但是,考虑到这些寄存器时间的时钟的时延控制的难度,我们不得不说:行波链上的时钟波动会变得极大,最终破坏整体时延要求,使得系统的整体工作时钟严重降低。