步进电机响应速度快、定位精度高、无积累误差、驱动电路及控制方法简单,在工业控制领域获得了广泛应用.但由于转动不够平稳,运行时会发生震荡现象,对系统的正常运行会产生不良影响,目前普遍认为最有效的解决方法是细分法.常用的细分法是用单片机实现或将细分参数存在EPROM 类非易失性存储器中通过逻辑电路实现细分输出,上述方法缺点是电路复杂、调试及研发周期较长.随着EDA技术的发展,目前已有将CPLD类可编程逻辑芯片用于步进电机细分控制器的尝试.本文采用FPGA可编程芯片及VHDL语言实现了对步进电机转角的十六细分控制,并在MAX+plus II平台上完成了设计及调试,由于FPGA芯片具有在系统编程的特点,不但使研发周期大大缩短,而且系统无需外接D/A转换器,电路简单,该方法为步进电机细分提供了一种新思路.

1 步进电机细分控制原理

所谓细分驱动就是把机械步距角细分戍若干个电的步距角,当转子从一个位置转到下一个位置的时候,会出现一些“暂态停留点”.这样使得电机启动时的过调量或者停止时的过调量就会减小,电机轴的振动也会减小,使电机转子旋转过程变得更加平滑,更加细腻,从而减小了噪声.

步进电机内合成磁场的幅值及两相邻合成磁场的夹角决定了步进电机旋转力矩的大小及步距角的大小,通过对步进电机励磁绕组中电流加以控制,使步进电机内部的合成磁场形成幅值不变、均匀的圆形旋转磁场,便可实现步进电机恒力矩及步进角均匀细分控制.

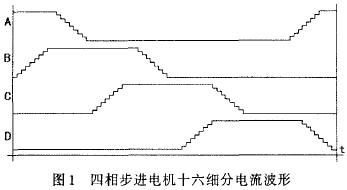

图1为本系统设计的四相步进电机的十六细分电流波形,一般情况下,总有两相绕组同时通电,一相电流逐渐增大,另一相逐渐减小.对应于一个步距角,电流变化16个台阶,也就是转子位置被细分成16个小角度,实现了一个步距角16细分的控制.

2 用FPGA实现四相步进电机十六细分的电路结构

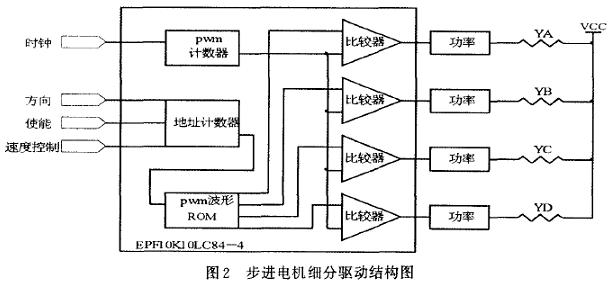

图2为步进电机细分驱动系统结构图.其中,PWM 计数器在时钟作用下递增计数,产生阶梯上升的周期性锯齿波,加载到各数字比较器的一端PWM 波形ROM输出的数据分别加载到各数字比较器的另一端.当PWM计数器的数值小于波形ROM输出数据时,比较器输出高电平,对应的功放模块导通,当PWM 计数器的数值大于波形ROM输出数据时,比较器输出低电平,对应的功放模块截止.随着波形ROM 中读出的数据变化,各比较器相应改变输出信号的高电平占空比,导致电机相应绕组上的通电时间变化,从而改变了绕组上的电流平均值,实现了细分控制.

3 十六细分驱动模块的设计

文中设计了用FPGA芯片(EPF10K10LC84-4)及VHDL语言实现一个十六细分步距角的步进电机控制电路自动按照以下控制方式运行:启动→匀加速→匀速→匀减速→停止.

3.1 十六细分驱动模块

细分驱动模块dianji是根据图2设计,在MAX+plus II平台下采用原理图编辑方法实现的.图3是FPGA内模块的电路图.其中compara4四位数据比较器电路及lpm-rom1PWM 波形ROM,都是采用LPM 元件定制实现,程序如下:

pwm_rom.mif文件

width=16;depth=64; --波形数据为16位,共64个

address_radix=hex;data_radix=hex; --地址和数据均用十六进制数表示

content begin --ROM 中的波形数据

0:8000;1:8100;2:8200;3:8300;4:8400;5:8500;6:8600;7:8700;8:8800;9:7800;a:6800;

b:5800;c:4800;d:3800;e:2800;f:1800;10:0800;11:0810;12:0820;13:0830;14:0840;

15:0850;16:0860;17:0870;18:0880;19:0780;1a:0680;1b:0580;1c:0480;1d:0380;1e:0280;

1f:0180;20:0080;21:0081;22:0082;23:0083;24:0084;25:0085;26:0086;27:0087;28:0088;

29:0078;2a:0068;2b:0058;2c:0048;2d:0038;2e:0028;2f:0018;30:0008;31:1008;32:2008;

33:3008;34:4008;35:5008;36:6008;37:7008;38:8008;39:8007;3a:8006;3b:8005;3c:8004;3d:8003;3e:8002;3f:8001;

end;

lpm_rom1的配置数据:艾件名为pwm_rom.mif,CNT16为三位输出的PWM 计数器,能产生八级阶梯波;CNT64为64进制计数器,作为PWM 波形ROM 的地址计数器,均用VHDL语言实现.

3.2 速度控制模块

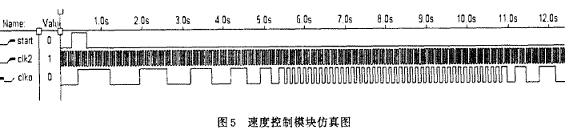

速度控制模块crea_clk又由五个子模块构成,如图4所示.其中SEL模块是时间控制块,当检测到start信号的上升沿后,它就会按顺序给U、N、D三个输出端输出一定时间的高电平,作为后续模块的控制信号,控制加速、匀速、减速各段的时间,UP、NORMAL、DOWN分别是匀加速、匀速和匀减速的时钟发生模块,GATE模块是时钟选通控制块,依据U、N、D三个信号的状态选通某一路时钟,作为细分驱动电路的波形ROM地址转换时钟信号,图5是该模块的仿真图.

结论

该控制模块在EDA仿真开发实验箱主板上已下载调试通过,驱动四相步进电机运行,验证了模块设计的正确性,由于FPGA内部为SRAM结构,在实际应用中,应外加EPROM类非易失性存储器保存控制程序。 ,并根据步进电机的转速、负载等参数合理选择晶振频率及驱动电路的输出功率等,方能取得好的控制效果.