几十年来,数字技术、计算机技术和永磁材料的迅速发展,为步进电机的应用开辟了广阔的前景。由步进电机与驱动电路组成的开环数控系统,既非常简单、廉价,又非常可靠。此外,步进电机还广泛应用于诸如打印机、雕刻机、绘图仪、绣花机及自动化仪表等。正因为步进电机的广泛应用,对步进电机的控制的研究也越来越多,在启动或加速时若步进脉冲变化太快,转子由于惯性而跟随不上电信号的变化,产生堵转或失步;在停止或减速时由于同样原因则可能产生超步。为防止堵转、失步和超步,提高工作频率,要对步进电机进行升降速控制。本文介绍一个用于自动磨边机的步进电机升降速控制器,由于考虑了通用性,它可以应用于其他场合。

从步进电机的矩频特性可知,步进电机的输出转矩随着脉冲频率的上升而下降,启动频率越高,启动转矩就越小,带动负载的能力越差,启动时会造成失步,而在停止时又会发生过冲。要使步进电机快速的达到所要求的速度又不失步或过冲,其关键在于使加速过程中加速度所要求的转矩既能充分利用各个运行频率下步进电机所提供的转矩,又不能超过这个转矩。因此,步进电机的运行一般要经过加速、匀速、减速三个阶段,要求加减速过程时间尽量的短,恒速时间尽量长。特别是在要求快速响应的工作中,从起点到终点运行的时间要求最短,这就必须要求加速、减速的过程最短,而恒速时的速度最高。而以前升速和降速大多选择按直线规律,采用这种方法时,它的脉冲频率的变化有一个恒定的加速度。在步进电机不失步的条件下,驱动脉冲频率变化的加速度和步进电机转子的角加速度成正比。在步进电机的转矩随脉冲频率的上升保持恒定时,直线规律的升降速才是理想的升降速曲线,而步进电机的转矩随脉冲频率的上升而下降,所以直线就不是理想的升降速曲线。因此,按直线规律升降速这种方法虽然简单,但是它不能保证在升降速的过程中步进电机转子的角加速度的变化和它的输出力矩变化相适应,不能最大限度的发挥电机的加速性能。本系统寻求一种基于FPGA控制的按指数规律升降速的离散控制算法,经多次运行,达到预期目标。

1 加减速控制算法

1.1 加减速曲线

本设计按照步进电机的动力学方程和矩频特性曲线推导出按指数曲线变化的升降速脉冲序列的分布规律,因为矩频特性是描述每一频率下的最大输出转矩,即在该频率下作为负载加给步进电机的最大转矩。因此把矩频特性作为加速范围下可以达到(但不能超过)的最大输出转矩来拟订升降速脉冲序列的分布规律,就接近于最大转矩控制的最佳升降速规律。这样能够使得频率增高时,保证输出最大的力矩,即能够对最大的力矩进行跟随,能充分的发挥步进电机的工作性能,使系统具有良好的动态特性。

由步进电机的动力学方程和矩频特性曲线,在忽略阻尼转矩的情况下,可推导出如下方程:

式中,![]() 为转子转动惯量,K为假定输出转矩按直线变化时的斜率,τ为决定升速快慢的时间常数,在实际工作中由实验来确定。fm为负载转矩下步进电机的最高连续运行频率,步进电机必须在低于该频率下运行才能保证不失步。(1)式为步进电机的升速特性,由此方程可绘制出电机升速曲线。(1)式表明驱动脉冲的频率f应随时间t作指数规律上升,这样就可以在较短的时间内使步进电机的转速上升至要求的运行速度。鉴于大多数的步进电机的矩频特性都近似线性递减的,所以上述的控制规律为最佳。

为转子转动惯量,K为假定输出转矩按直线变化时的斜率,τ为决定升速快慢的时间常数,在实际工作中由实验来确定。fm为负载转矩下步进电机的最高连续运行频率,步进电机必须在低于该频率下运行才能保证不失步。(1)式为步进电机的升速特性,由此方程可绘制出电机升速曲线。(1)式表明驱动脉冲的频率f应随时间t作指数规律上升,这样就可以在较短的时间内使步进电机的转速上升至要求的运行速度。鉴于大多数的步进电机的矩频特性都近似线性递减的,所以上述的控制规律为最佳。

1.2 加减速离散处理

在本系统中,FPGA使用分频器的方式来控制步进电机的速度,升降速控制实际上是不断改变分频器初载值的大小。指数曲线由于无法通过程序编制来实现,可以用阶梯曲线来逼近升速曲线,不一定每步都计算装载值。

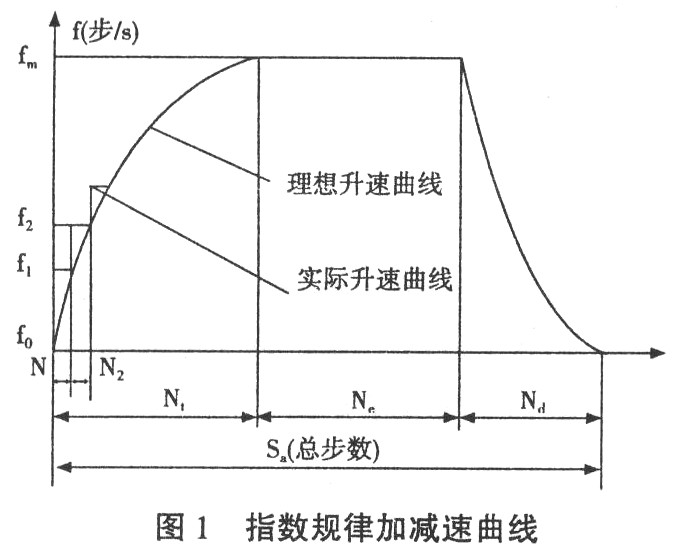

如图1所示,纵坐标为频率,单位是步/秒,其实反映了转速的高低。横坐标为时间,各段时间内走过的步数用N来表示,步数其实反映了行程。图中标出理想升速曲线和实际升速曲线。

步进电机的升速过程可按以下步骤进行处理。

(1)若实际运行速度为fg,从(3.4)式中可算出升速时间为:

![]()

(2)将升速段均匀地离散为n段即为阶梯升速的分档数,上升时间为tr,则每档速度保持时间为:

程序执行过程中,对每档速度都要计算在这档速度应走的步数,然后以递减方式检查,即每走一步,每档步数减1。当减至零时,表示该档速度应走的步数己走完,应进入下一档速度。一直循环到给出的速度大于或等于给定的速度为止。减速过程与升速过程刚好相反。

2 频率脉冲的实现

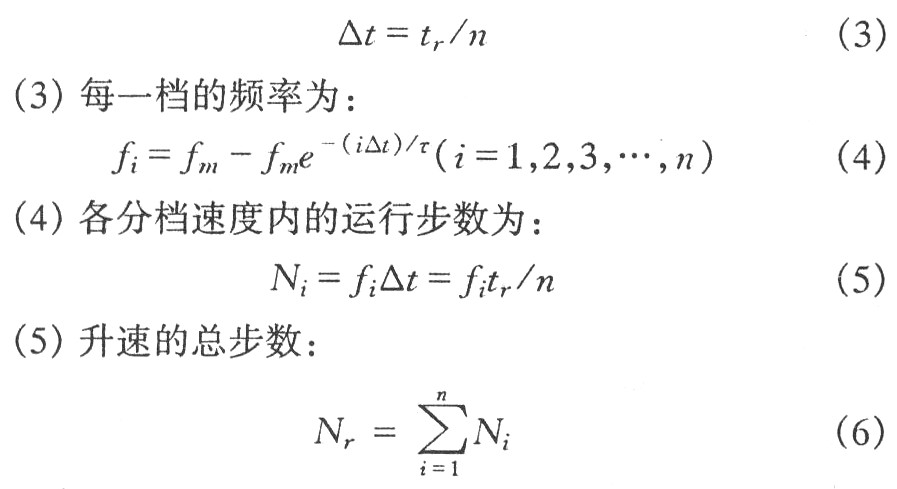

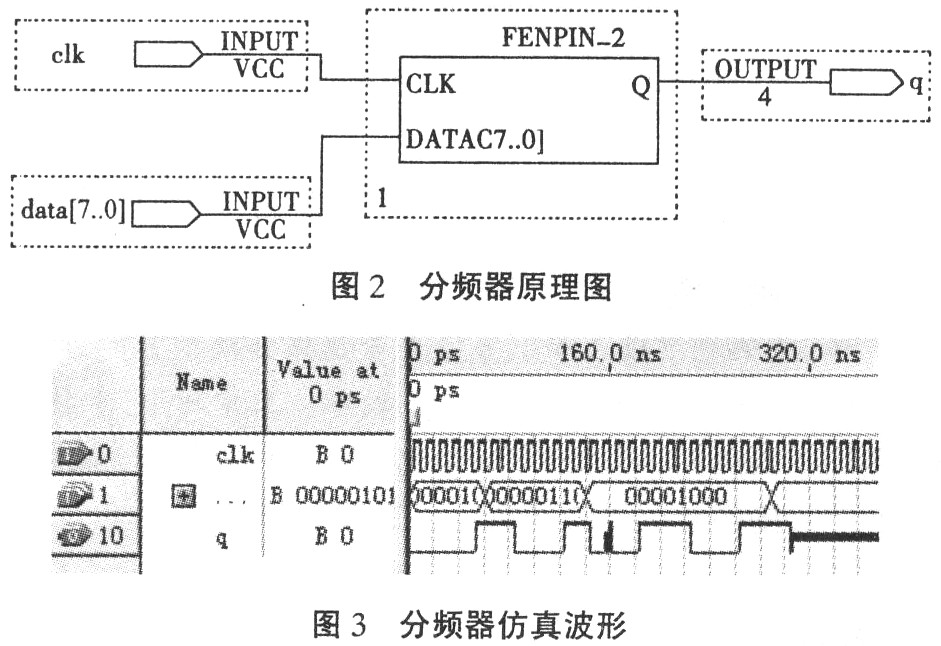

频率脉冲模块的核心是可控分频器,由外部的晶振产生标准频率,只要在分频器的输入端输入相应的分频系数,就可以得到所需的频率。本模块是利用VHDL硬件描述语言,通过QuartusII开发平台,使用Altera公司的FPGA,设计了一种能够满足上述各种要求的较为通用的可控分频器。图2为分频器的原理图,图3为分频器的仿真波形图。

3 结语

基于硬件描述语言VHDL设计的控制器具有开发设计周期短、风险低、系统集成度高、功耗低等优点,将是芯片设计的主流方向。开放式数控系统中,研究实现能硬件复用的加减速模块以及相关功能模块,利用可编程逻辑器件FPGA的可重构能力,能按需求灵活实现功能全定制的运动控制芯片。本文设计了自动磨边机中的指数加减速控制器。在此基础上,只需扩展相应个数的加减速模块即可实现多轴联动加减速控制。