在工业能耗中,三分之二以上的能耗来自工业电机驱动设备,因此,在工厂费用开支中,高效的电气特性是非常重要的因素。在电机驱动系统中采用速率可变驱动器 (VSD) 来替代传统的驱动器能够显著提高效率,能耗节省了近 40%。在电机控制设计中,设计人员可充分利用 Altera® FPGA 强大的适应能力、精度可调数字信号处理 (DSP) 以及集成系统设计工具等优势,使用VSD 系统的高效平台。

性能调整和集成优势

很多商用 MCU 或者 DSP模块具有通用驱动工作基本单元。但是,这些器件存储器有限,模拟范围较窄,脉冲宽度调制(PWM) 通道数量有限,对多轴系统的支持不足。下一代驱动功能对性能的要求更高,需要提高电机效率,所采用的平台应具有性能调整功能,以满足处理和DSP 需求,同时能够灵活的集成并优化系统。

图1 电机控制 FPGA优化设计流程

FPGA 很容易根据应用需求来调整性能。设计人员可以在 FPGA 中嵌入多个处理器或者使用灵活的 DSP功能,然后,采用其他的逻辑、定制指令或者所支持的多种工业网络协议。设计人员利用Altera FPGA可以实现多种嵌入式处理器,独立控制每一个子系统。Altera FPGA的并行特性支持电机控制系统构建模块的集成。例如,Altera Nios® II嵌入式处理器 (32位RISC软核处理器)可以控制各种接口以及传感器和编码器。设计人员可以使用精度可调浮点 DSP模块完成磁场定向控制 (FOC)或者其他需要大量数学计算的算法。

图2所示为能够集成到 FPGA中的各种单元,用于建立一个“单芯片驱动”系统。集成IP功能能够并行运行,保证了在顺序操作或者延时操作中不会出现瓶颈。

图2 FOC模型包括复杂数学算法

这一设计流程支持IP的集成,包括:

• 位置反馈——具有高精度位置反馈功能的编码器,例如,EnDAT、Hiperface,以及BiSS,支持 10倍速和位置数据。

• IGBT控制——使用绝缘栅极双极晶体管 (IGBT),切换到驱动 AC电机所需要的高电压。在 IGBT的栅极输入上使用空间矢量调制(SVM)技术,产生驱动电机所需要的正弦电压波形。IGBT可以是 2级或者 3级变量。

• ADC接口——与外部模数转换器(ADC)连接,测量电机的反馈电流。很容易将Sigma delta (SD) ADC与大驱动电压实现光电隔离,降低噪声,支持 FPGA对其输出进行采样,实现快速精确的读取操作。

• 网络接口——在 FPGA中实现实时协议,以适应实际应用所需要的工业以太网协议标准,例如,Ethernet/IP、PROFINET IO/IRT和 EtherCAT。工业以太网在工业驱动中的应用越来越广泛。

这些基于 DSP的电机控制功能、通信以及接口标准的大量应用使得FPGA成为工业电机驱动的理想平台。

处理复杂数学算法

各种驱动技术的差别很大,具体取决于电机类型及其应用。例如,控制电泵和风扇的驱动器有不同的要求和反馈机制,以便控制 CNC电机或者封装设备。从这些编码器和传感器中采集到的数据被反馈到控制系统中,用于进行数学计算,以确定目标系统负载和扭矩的电压电平。

例如,常用的永磁体同步电机 (PMSM)使用需要大量数学算法的 FOC功能作为控制环算法的一部分,该功能也称为矢量控制。在需要精确扭矩控制的工业伺服电机中,也经常采用FOC。FOC技术有助于减小电机体积、成本和功耗。FOC精确的测量电压电平以及相应的电机速度,更好的控制速度和扭矩,即使负载变化了也能够提供恒定扭矩。此外,FOC还减小了扭矩波纹和电磁干扰。但是,如图3所示,这一数学模型非常复杂,高速运行这一算法时需要很强的计算能力。

FOC涉及到对电机正弦 3相电流的实时控制,以建立平滑的旋转磁通量码型,其旋转频率对应于正弦波的频率。该方法控制电流矢量的振幅,将其维持在相对于转子磁通量轴 90度的位置(“正交”电流)。这样,设计人员可以控制扭矩,同时将直流电流分量(0度 )保持在零。这一算法涉及到以下步骤:

1. 使用Clarke和Park变换,将编码器的3相反馈电流输入和转子位置转换为正交和直流电流分量。

2. 使用这些电流分量作为两个并行运行的比例和积分(PI)控制器的输入,将直流电流限制为零,把正交电流保持在所需的扭矩水平上。

3. 通过Clarke和Park反变换,将PI控制器的直接和正交电流输出转换回3相电流。

Altera FPGA提供一款精度可调DSP模块,能够灵活选择满足要求的精度级,而且还支持单精度和双精度浮点类型。这些因素使得 DSP模块成为实现 FOC环和其他复杂数学算法的理想选择。集成DSP模块是很多Altera 28-nm FPGA体系结构所具有的特性,支持每一模块在编译时配置为18位或者高精度模式。

利用功能强大的开发工具

优化电机控制设计需要通用工具(以及实用的工具流程 )对系统进行建模和仿真,实现低延时复杂算法,将系统集成在一起,精确的调整性能,以满足电机驱动的实际需求。设计人员使用集成工具流程(图4所示),能够缩短开发时间,提供更灵活、功能更强大的模型,以适应不同类型的驱动系统。

图3 FOC模型

图4 电机控制 FPGA优化设计流程

Altera为嵌入式工业设计人员提供功能强大而且使用方便的开发工具,例如, Quartus® II设计软件和 MegaCore® IP库。Altera还提供系统集成工具,例如Qsys 或者 SOPC Builder实现面向任务的操作,以及 DSP Builder来优化 DSP。此外, Altera提供基于 Eclipse的Nios II嵌入式设计套装 (EDS),更方便的通过设计流程来完善 FPGA硬件。

Nios II嵌入式设计套装

Altera 提供基于 Eclipse的 Nios II EDS、Nios II嵌入式处理器等功能强大而且使用方便的嵌入式开发工具,支持标准操作系统(OS)以及来自多家流行供应商的实时操作系统(RTOS)。Nios II EDS 支持包含多个通用32位RISC 软核处理器的工程的开发。这些处理器的性能高达 340 MIPS(Dhrystones 2.1),可以独立拥有各自的定制指令集、数据通路和地址空间。

Qsys和 SOPC Builder系统集成工具

Altera的 Quartus II开发软件包括最新的 Qsys(以及传统的 SOPC Builder)系统集成工具。这些工具有助于设计人员自动完成硬件组件集成任务,定义并生成完整的芯片系统(SoC)。Qsys或者 SOPC Builder并不是使用传统的设计方法来手动定义和连接HDL模块,而是在GUI中帮助您定义系统组件,然后自动生成互联逻辑。这些工具生成定义系统中所有组件的 HDL文件,然后,顶层HDL文件将所有组件连接起来。这些工具生成 Verilog HDL或者 VHDL。

这些系统集成工具使用Avalon®接口来连接逻辑器件(片内或者片外)。在电机系统中,Avalon接口连接软核处理器以及驱动系统的其他单元。这降低了系统集成的复杂度,实现了连续直观的最优系统。互联架构支持通过从机侧仲裁进行同时多主机处理,从而管理这些连接。这些工具在每一从机端口前插入仲裁模块,以满足不同主机的要求,从主机和从机端口中提取出系统详细的互联信息。图5显示了连接系统中多个从机和主机的互联架构。

图5 采用Qsys或者SOPC Builder管理系统互联

Altera的系统集成和嵌入式开发工具帮助设计人员迅速实现处理器与使用DSP Builder开发的硬件加速电机控制算法之间的接口连接。

DSP Builder和 MATLAB/Simulink

电机控制系统设计人员可以采用FPGA中的DSP功能来实现需要大量数学功能的高速电机控制算法。Altera的 DSP Builder在友好算法开发环境中,帮助设计人员生成 DSP设计的硬件表征,缩短了 DSP设计周期。DSP Builder结合了 MathWorks MATLAB®和 Simulink®系统级设计工具以及 Altera Quartus II软件和第三方综合和仿真工具,实现算法开发、仿真和验证功能。设计人员可以组合使用 Simulink模块和 DSP Builder模块以及 IP模块,验证系统级规范,进行仿真。

利用 Altera的集成 DSP Builder工具,设计人员在 MATLAB/Simulink环境中直接对FOC算法进行建模,构建结构图,连接表示系统的基本模块,如图6所示。这一实例中使用的基本模块是 ADD、SUB、MULTIPLY、CONSTANT、COSINE和 SINE。Simulink支持您对模型或者系统算法行为运行比特精度数学仿真。完成了算法开发后,DSP Builder针对您所选择的Altera FPGA器件,自动生成流水线RTL并进行优化。

图6 永磁体同步电机的 FOC实例

这一设计实例还包括位置和速度控制环,支持对转子速度和角度的控制,如图7所示。典型的电机控制 IP系统包括空间矢量 PWM、电流和扭矩控制环以及速度和位置控制环。根据 FPGA和CPU资源的使用情况,设计人员在硬件和软件之间分配这些单元。

图7 永磁体同步电机的位置、速度和FOC控制器

一个典型的传统设计流程包括建立电信号和电机系统模型,通过仿真开发算法,然后,编写C程序,实现算法,在 DSP模块上运行。这一设计流程具有以下缺点。

• 通常以浮点方式实现算法建模,然后转换为定点方式,在 DSP模块中实现。一般以手动方式实现浮点到定点的转换,缩放和上溢保护功能非常复杂。

• 必须针对模型重新验证 C程序。

• 提高算法运行时性能还需要进行以下步骤:

a.手动优化C程序以提高性能。

b.更新到速度更快但是更昂贵的 DSP模块。

c.在多个DSP模块上并行运行算法(如果可能)。

设计人员可以采用 DSP Builder,优化基于 FPGA的 DSP系统设计。DSP Builder优化流水线以及共享资源,生成高效的RTL表征。您可以组合使用现有的 MATLAB功能和Simulink模块以及Altera DSP Builder模块和其他IP内核,连接系统级设计,实现DSP算法开发,如图8所示。利用DSP Builder,系统、算法和硬件设计人员可以共享公共开发平台。

图8 DSP Builder系统级设计

注释:

(1)所使用的PI控制器需要反馈通路以支持要计算的整数部分。这一通路位于DSP Builder模型外部,通过连接测试台和生成的 VHDL中的 I_out端口和相应的 I_in端口来实现。

DSP Builder高级模块库自然支持定点或者单精度和双精度浮点类型的算法建模。设计人员可以使用比要求更高的精度,先在 Simulink中对算法建模,然后,在工具中调整精度,以满足最终要求。DSP Builder具有以下优势:

• 采用高级模块库,以按键FPGA方式实现算法。不需要手动转换步骤。

• 在硬件中运行之前,在 Simulink中直接观察运行时延时、数据吞吐量以及算法应用。采用 Simulink进行设计空间研究,选择最合适的实现方式。

• 在生成时优化并调整基本算子,包括 SQRT和三角等函数,在软件中实现这些算子时,其运行较慢而且时间可变。这一方法提供了可预测的算法运行时间,显著加速了某些算子的运行。

FOC算法基准测试

为展示这些特性和功能,Altera开发了一个基准测试练习,以仿真 FOC算法,对比标准非折叠和折叠实现的结果。FOC算法包括 Park/Clarke变换以及 PI控制模块,它需要加法 /减法、乘法、Sin、Cos算子以及某些常数和饱和逻辑,如图9和图10所示。在一个典型的 FOC控制器中,以 10-100ksps速率对输入进行采样,100MHz FPGA时钟速率很容易达到这一速率要求。在100ksps时,每10ms必须处理一个新采样。将这一处理延时常数保持在最小值,有利于提高控制算法的性能。

测试台包括图10 所示的单元:

图9 简单PI控制器

图10 永磁体同步电机位置、速度和磁场定向控制的控制器

• 输入激励(绿色 )——提供控制输入(位置申请 )

• 电机模型(蓝色)——对PMSM电机进行建模

• DSP Builder位置速度FOC控制器(橙色)——对控制算法进行模型

采用DSP Builder 进行设计调整

设计人员可以从MATLAB 工作空间变量中控制关键系统参数,调整设计:

• 折叠因子——扫描延时、吞吐量以及资源使用情况,找到最佳实现点。

• 定点算法精度——观察算法中不同级精度调整的影响,以提高算法性能和资源利用率。

• 算法调整——相对于设备(电机)的物理模型仿真实际算法,调整PID控制器、滤波器的参数,在模型级进行观察。

基准测试结果

下面详细介绍通过在 Simulink中建模所获得的算法基准测试结果,在 Cyclone® IV器件中使用了单精度浮点和定点类型。结果表明,设计实例满足所需要的 100MHz时钟速率、资源利用率以及算法延时要求。

在Quartus II软件中成功进行编译后,设计人员点击Simulink图中的Quartus模块链接,可以获得正确的资源使用信息。

一般而言,以定点方式来实现不需要浮点大动态范围的设计。但是,浮点实现避免了算法开发和调整过程中出现的算法上溢问题。

默认情况下,DSP Builder建立一个全流水线VHDL表征,可以在每一时钟周期中接收新输入值。然后,对比这一“非折叠”配置结果与“全折叠”配置结果。

如图11所示,表1中的结果表明,由于采用了折叠因子,显著减少了算子数量,因此,可以使用低密度 Cyclone IV器件。而且,对于算法而言,增加的延时是可以承受的。控制环的速度是算法延时加上建立时间。在5ms时,结果是每秒200K循环(或者PWM输出),完全满足所需的规范要求。

表1.折叠因子的优点

表2.定点浮点对比

注释:

(1)浮点结果使用了浮点正弦。使用定点实现,占用的LE资源减少了4K LE,乘法器减少了16个。

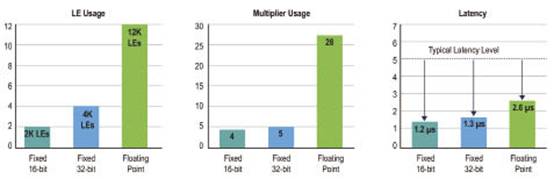

DSP Builder同时支持定点和浮点实现。表2和图12对比了“全折叠”定点和浮点实现所需要的资源。使用 MATLAB工作空间变量来控制定点精度,支持设计人员进行简单的试验。

图11 系统资源和延时——没有折叠以及 100倍折叠

图12 系统资源和延时——定点和浮点

结果总结

从基准测试试验中得到了以下结论:

• 使用FOC模型和浮点精度对LE资源使用的确有一些影响。但只是稍微增加了一些延时(不到5ms),对于运算而言,延时是可以接受的。

• 精度降低到16位也减少了对资源的使用,这是因为有较窄的数据通路。

• 折叠因子提高了硬件资源使用率,同时满足了 1-Msps的吞吐量。这样,可以实时处理10通道的100-ksps FOC算法。

总结

在下一代电机控制系统中,对目前的现代 MCU和 DSP模块性能要求越来越高。设计人员要求能够灵活的调整电机控制算法,以降低成本和功耗。商用 DSP解决方案的定点和浮点能力有限,不能适应驱动系统所需其他组件的要求。

相反,Altera FPGA支持组件集成,例如,能够管理所有操作的处理器,灵活方便的连接定制子系统,优化设计流程,从而简化了复杂并行电机控制环和算法。电机系统结合了各种快速控制环、定时输出脉冲频率以及多传感器接口和滤波功能。Altera FPGA内置了并行处理功能,提供高性能精度可调 DSP模块,从而解决了电机控制系统遇到的难题,为其提供良好的解决方案。除了这些内在的 FPGA优势,Altera还提供更好的设计方法。在建模时使用 MathworksSimulink/MATLAB工具,Altera的 DSP Builder对电机算法进行优化,Qsys或者 SOPC Builder实现系统集成,Quartus II软件用于设计综合和布局布线,实现了全面的集成设计方法,从而能够处理复杂的驱动系统。