1 1553B概述

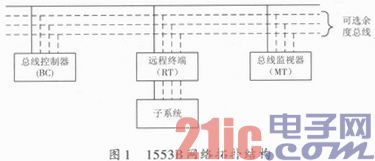

MIL-STD-1553B是美国于20世纪70年提出的一种用于战机的时分控制/命令响应式总线。1553B的网络拓扑结构如图1所示,它最多可以挂载32个终端,所有消息共享一条线路,通过采用冗余设计,另一条线路始终处于热备份状态,大大提高了可靠性。其字长20 b,数据有效长度16 b,最大信息量长度为32个字,传输速度为1 Mb/s,传输方式为半双工方式,采用曼彻斯特Ⅱ型码。1553B的3种终端类型为:

(1)总线控制器(Bus Controller),总线系统中惟一被安排为执行建立和启动数据传输任务的终端。

(2)远程终端(Remote Terminal),子系统到总线的接口,在BC的控制下实现命令、数据的接收和发送。

(3)总线监视器(Bus Monitor),能记录总线上的所有数据,方便备份和查错,但不参与总线通信。

由于1553B具有可靠性高、实时性好、扩展方便等优点,被广泛应用于飞机、导弹、卫星、舰艇等航空航天和兵器领域。目前,航天系统大多采用DDC公司的BU-61580/BU-65170协议芯片来实现1553B通信。BU-61580是一款多协议集成接口芯片,由两个低功耗双端收发器、协议逻辑、存储器管理逻辑、处理器接口逻辑及4K×16 B内置共享静态RAM以及直接面向主处理器的缓存接口组成,能完全实现1553B标准所规定的所有信息传输方式。BU-61580和BU-65170的区别在于前者集成了BC/RT/BM功能,后者只能实现RT功能。在此研制的某型号项目作为一个子系统,只要求实现RT功能。因此,选用了BU-65170作为1553B协议芯片。

一般采用CPU来控制BU-65170实现1553B通信,然而CPU只能顺序地执行命令,系统硬件不扩展的情况下,难以实现更加复杂的数据处理和控制。随着航天载荷小型化的要求,数据的运算处理,系统的运行控制及通信,更多地采用FPGA实现,这样就可以把所有功能集成在一片FPGA芯片中,还能实现代码的重复利用,提高研发效率。本文采用Xilinx xc6slx75控制BU-65170实现1553B通信,同时因工程项目需要又用FPGA实现了RS422通信,这样不仅方便测试,使结果直观可见,还使整个系统事实上成为了1553B总线和RS 422总线适配器。只要稍稍修改代码,就可以在保留数据处理的功能下将系统移植应用到采用其他通信方式(如RS 232,LVDS等)的子系统上。

2 硬件设计

BU-65170共有70个信号管脚,其中主要的控制信号如表1所示。

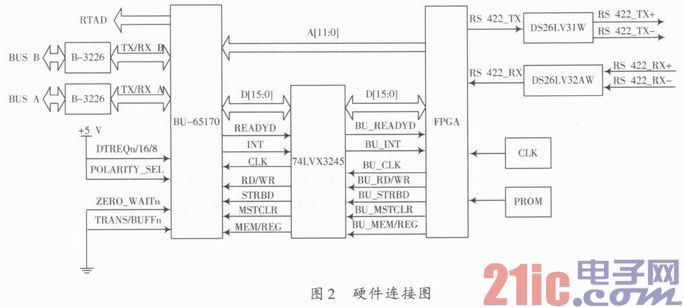

Xilinx的Spartan-6系列xc6s1x75芯片拥有74 637个逻辑单元,11 662个可配置逻辑模块,280个I/O口以及18 KB的Block RAM模块,同时拥有丰富的时钟管理模块(CMT)、集成存储器控制模块等,数据速率高达800 Mb/s。采用XCF32P Flash芯片作为FPGA的PROM,使用MASTER配置模式,这样在每次上电时程序都会写入到FPGA中。由于FPGA的I/O口是3.3 V逻辑,而BU-65170是+5 V逻辑,所以需要采用电平转换芯片74LVX3245进行FPGA和BU-65170之间的逻辑电平转换。系统的硬件连接如图2所示。

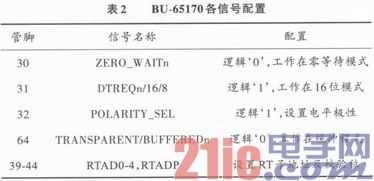

BU-65170有4种接口模式可以选择,采用16位零等待模式。在此模式下,FPGA接收到BU-65170的READYn信号为低电平后,表示D15-D00上已经呈现读取的数据,或者D15-D00上的数据已经写入存储器或寄存器。BU-65170各信号配置如表2所示。

分别采用DS26LV32AW和DS26LV31W芯片作为RS 422差分接收器和驱动器,UART设计将在逻辑设计中详细介绍。

3 逻辑设计

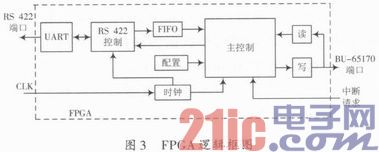

使用Verilog HDL进行编程,在FPGA中实现所需的功能。逻辑总体框图如图3所示,下面分别对各个模块进行详细介绍。

3.1 读/写模块

根据芯片手册给出的CPU读写时序图编写程序,在FPGA中实现对BU-65170寄存器和内部RAM进行读写的模块。读写模块的仿真时序图如图4和图5所示。

在读写过程中,信号BU_RD_WR为‘1’时表示对BU-65170进行读操作,为‘0’时为写操作;信号BU_MEM_REG为‘1’时表示对内部RAM进行读/写,为‘0’时表示对寄存器进行读/写。在零等待模式中,信号BU_STRBD和BU_SELECT(可与BU_STRBD绑定,所以没有给出)控制着读/写操作的开始。

在长STRBD模式下SELECT和STRBD同时为低电平的第2个CLK上升沿,内部锁存MEM_REG和RD_WR信号;短STRBD模式下STRBD上升沿内部锁存MEM_REG和RD_WR信号。考虑到容易满足时序要求,采用长STRBD模式。当BU-65170锁存住MEM_REG或RD_WR信号后,BU_READY会出现一个上升沿,紧接着当BU_READY出现下降沿时,表示BU-65170内部传送周期已经结束。

在16位零等待模式下,写一个内部存储单元或寄存器时,只需执行一次写操作,使该字的地址和数据呈现在地址总线和数据总线上即可。而读一个内部存储单元或寄存器时,需要进行两次读操作。第一次读时,要读单元的地址和位置出现在A13-A00和MEM_REG上,这个周期独处的数据应忽略掉;第二次读时,相应的数据会出现在数据总线上。

因此,如果FPGA要执行一个多字读操作,地址总是早于对应的读出数据,在同一个周期上,地址总线上出现下一个字的地址,数据总线上出现前一个字的读出数据。

3.2 配置模块

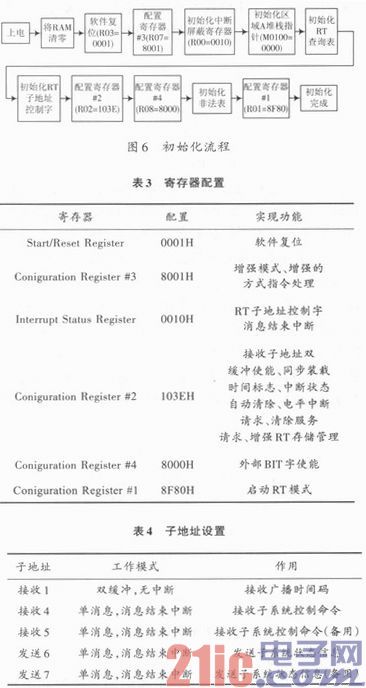

BU-65170有17个寄存器,通过配置这些寄存器来选择工作模式和具体功能。选择增强模式、增强中断使能模式,使能RT子地址控制字中断,服务请求自动清除。初始化流程如图6所示,寄存器详细配置如表3所示,具体子地址设置如表4所示。

3.3 时钟模块

使用40 MHz的外部晶振作为FPGA的时钟输入,然后用FPGA自带DCM模块分频得到16 MHz主时钟,作为其余模块的全局时钟,仿真和实际波形测试表明全局时钟稳定性良好,满足系统要求。

3.4 RS 422控制及UART模块

RS 422模块实现了RS 422通信功能,一方面满足了工程要求;另一方面也使调试1553B系统变得方便明了,因为1553B发送过来的数据可以立即通过RS 422转RS 232接口显示在PC机上,同理,可以通过PC机发送数据到1553B的总线控制器。1553B总线接收数据的过程如下:RS 422端口发送数据到FPGA,将数据缓存在FIFO中,RT接收到发送命令后,FPGA把FIFO中的数据写入RT相应的发送子地址,最后再由RT发送给BC。类似地,1553B总线发送数据的过程如下:RT接收到接收命令后,FPGA立刻把数据从相应子地址读出,并传送给RS 422模块,再通过UART将数据发出。

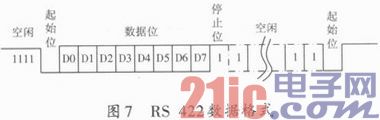

UART采用10位异步通信方式,即1个起始位,8个数据位,1个停止位,如图7所示,波特率为9 600 b/s。RS 422控制模块内部包含一个分频模块,将产生RS 422接口定义中的收发所需的波特率。通过对于系统时钟的分频,产生波特率为9 600 b/s和153 600的信号。

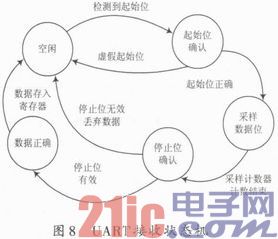

接收状态机见图8。当检测到起始位时,首先检验起始位是否正确,如果正确,立即采样数据位,否则就返回空闲状态。当采样计数器计到8后判断下一位是否为停止位,若不是,则丢弃数据并进入空闲状态;若是,则把数据存入寄存器后进入空闲状态,结束一次成功的接收。为了提高正确率,还采用三模冗余算法。UART发送过程与接收类似,在收到发送信号后将需要发送的数据存入缓存,在使能有效和缓存不空的情况下开始传输。此时指针开始计数,首先发送起始位‘0’,接着一次发送8 b数据,最后发送停止位‘1’,结束一次发送过程。

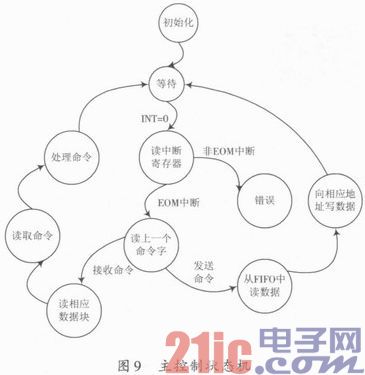

3.5 主控制器

FPGA中控制与BU-65170通信的主控制状态机如图9所示。初始化完成后程序进入等待状态。此时如果收到中断信号(INT=0),则首先读取中断寄存器,判断是否为消息结束中断(EOM),如果不是,进入错误状态,等待BC对RT进行检查或重启RT;如果是消息结束中断,则继续读取上一个命令字,若是发送命令,则从FIFO中读取28 B的状态信息数据,接着向相应的发送子地址数据块填写数据,在RT收到下一个发送命令后,BC从相应子地址读取上一条数据,这与对BU-65170进行读操作的原理相似。如果上一个命令字是接收命令,则读取相应子地址对应的数据块,然后读取具体命令内容,再根据命令进行相应的处理,最后回到等待状态。

接收子地址1工作在双缓冲模式,用于接收BC发送的广播时间码,加载到每一条从RT发送到BC的状态信息的头部。双缓冲模式可以使FPGA访问指定子地址刚接收到的消息,RT将接收的数据字交替存储到数据块0和数据块1中。当FPGA需要访问接收子地址1内的消息时,首先将其改成单消息模式,读取数据块地址,并将其bit5的值取反得到“非活跃”数据块的地址,读取其上的最新时间码后再将接收子地址1改为双缓冲模式。

4 测试

选用Alta公司的ECD54-1553多功能板卡(能模拟BC\RT\BM)作为BC,与设计的RT搭成一个测试系统,如图10所示。

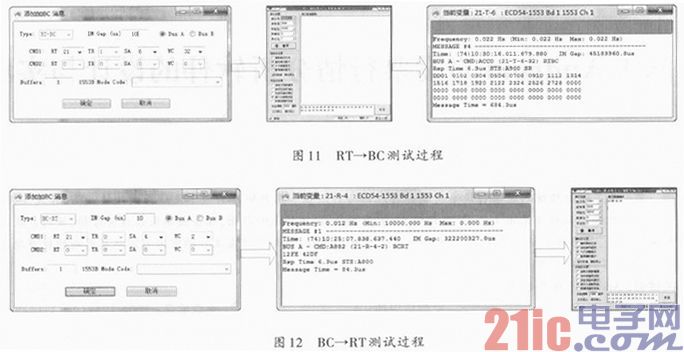

首先在ECD54-1553的控制界面中设置RT地址为21,然后根据在FPGA逻辑中设定的RT子地址及传输数据量进行相应的设置,再开启总线监控(BM)功能,测试RT→BC的过程如图11所示。设置RT地址为21、发送子地址为6、数据量为32个字(2 B标志位+28 B数据+2 B保留位);通过串口调试助手从PC机向RS 422发送28 B数据;经过FPGA处理后传送给1553B总线控制器,BM显示总线控制器正确收到从RS 422发来的数据。测试BC→RT的过程如图12所示。

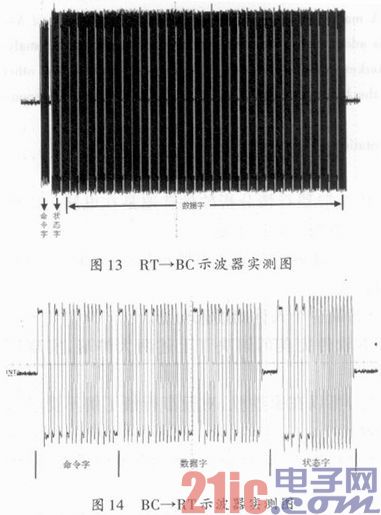

设置RT地址为21、接收子地址为4、数据量为2个字;由BC发送2个字的数据12FE 42DF;串口调试助手显示RS 422正确接收到BC发送过来的数据。示波器测得的实际曼彻斯特Ⅱ型码波形如图13,图14所示。

测试结果表明RT能正确、稳定地跟BC进行通信,达到工程项目所需的要求。

5 结语

本文设计了基于FPGA和BU-65170的1553B远程终端,实现1553B通信。详细介绍了硬件连接、BU-65170芯片配置、FPGA逻辑模块、UART设计、测试过程和结果。通过引入RS 422接口,更加直观地观测到1553B通信过程,易于调试。采用FPGA的最大优点是能迅速移植代码,缩减研发周期。随着技术的发展,对数据传输和处理提出了更高的要求,未来可以把控制其他子系统的模块和数据处理功能集成在一块FPGA芯片中提高集成性,便于开发和维护。