调试载波通信系统的时候遇到这样一个问题:两台设备分别为A何B,他们都使用了定时器2~4来进行通讯,A设备的PCLK1配置为HCLK,而B设备的PCLK1配置为1/2HCLK,通讯过程发现A,B两个设备偶尔能通讯偶尔不能通讯,表现出通讯部稳定。理论上应该完全不能通讯才是,深入研究STM32F101C8T6的数据手册发现问题所在,截图如下:

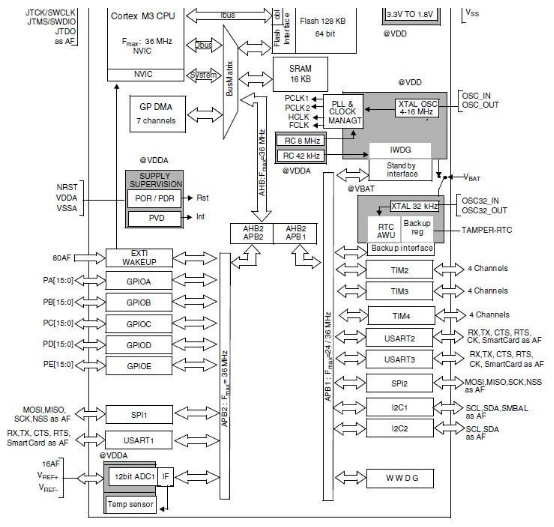

图1 STM32功能框图

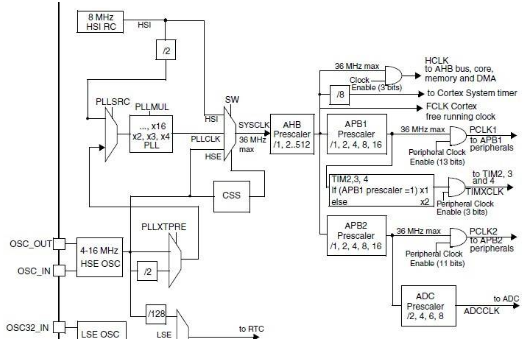

图2 STM32时钟系统

从图1可以看到APB1总线挂接了TIM2~4,UART2~2...WWD等设备。然后从图2中可以看到只有外设直接使用了APB1的时钟作为实际时钟,而TIM2~4根据APB1的时钟进行了调整。因此当设备B的PCLK1配置为1/2HCLK时实际上就是将APB1配置为了1/2HCLK,此时因为APB1的分频系数不为1,因此TIM2~4使用的时钟自动2倍频,实际频率就是HCLK了。由于先2分频再2倍频理论上是和HCLK一致,但电路结构等因素将导致得到的结果和直接赋予HCLK不完全一致,导致通讯不稳定。最终通过调整A设备的PCLK1也为1/2HCLK,可以稳定通信。