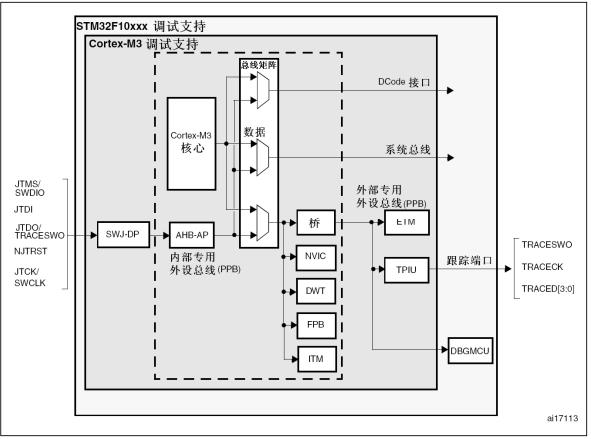

OBG在单片机中的解释STM32单片机的内核(Cortex-M3)含有硬件调试模块,支持多种复杂的调试操作,硬件调试模块允许内核在取地址或者访问数据时停止-这就是我们在单片机开发和过程中可以在线仿真的保障。内核在停止时,其内部的状态与外部状态都是可以进行查询的,- 在单片机仿真调试中受到中断,通常为人为设置的断点,此时单片机中所有的变量,以及程序指针,CP,等地址指针都可以查询到状态。在调试过程中,设置了断点,当程序停止运行时,我们可以接着进行单步执行,跳出函数,进入函数等操作。还可以进行复位,使寄存器都回归到初始复位状态。

OBG调试接口

串行接口

JTAG调试接口

OBG调试框图

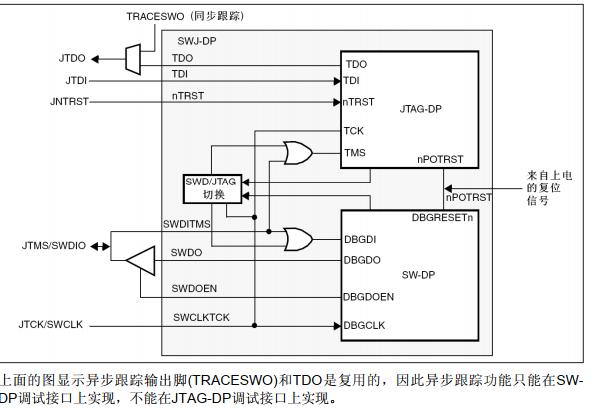

SWJ(serial wire and JTAG)调试端口

JTAG调试接口(JTAG-DP)为AHP-AP模块提供5针标准JTAG口串行调试接口(SW-DP)为两针接口(时钟+数据)接口在swj-dp接口中,SW-DP接口的2个引脚和JTAG标准接口的5个引脚中的一些是复用的。

SWJ调试端口

JTAG-DP与SW-DP切换的机制 JTAG调试接口是默认的调试接口如果想换到SW-DP,必须在TMS/TCK上输出一指定的JTAG序列(SWCLK SWDIO),该序列禁止JTAG-DP,并激活SW-DP,该方法只能通过SWCLK与SWDIO两个引脚来激活。

指定序列是:

输出超过50个SWCLK的周期=1信号

输出16个SWDIO信号0111100111100111(MSB)

输出超过50个SWCLK周期的=1信号

注:如果在调试过程中,使用到了SW-DP模式,可以对SWDIO与SWCLK信号进行观察,不出意外可以观察到上面的信号。

SWJ调试端口脚 注:下图中的所有引脚在所有STM32系列单片机中都存在SWJ端口对应

在系统复位后(SYSRESETn或PORESETn)以后,属于SWJ-DP的所有5个脚都立即被初始化为可被调试器调用的专用引脚。然而STM32控制器可以复用重映射和调试IO配置寄存器(AFIO_MARR)寄存器来禁止SWJ-DP接口的部分或者全部引脚功能,被释放为普通IO口,此寄存器被映射到Cortex-M3系统总线的APB桥上,对此寄存器的配置将由用户进行配置。

注:在单片机开发中基本上以及绝对不会用到占用调试接口的情况。大家松口气JTAG脚上的内部上拉与下拉保证JTAG的输入引脚不是悬空的是非常必要的,因为他们直接连接到D触发器控制着调试模式。必须特别注意SWCLK/TCK引脚,因为他们直接连接到一些D触发器的时钟端。

为了避免任何未受控制的I/O电平, STM32F10xxx在JTAG输入脚上嵌入了内部上拉和下拉●JINTRST:内部上拉

● JTDI:内部上拉

● JTMS/SWDIO:内部上拉

● TCK/SWCLK:内部下拉

一旦JTAG I/O被用户代码释放, GPIO控制器再次取得控制。这些I/O口的状态将恢复到复位时的状态。

● JNTRST:带上拉的输入

● JTDI:带上拉的输入

● JTMS/SWDIO:带上拉的输入

● JICK/SWCLK:带下拉的输入

● JTDO:浮动输入

软件可以把这些I/O口作为普通的I/O口使用。

注意: JTAG IEEE标准建议对TDI, TMS和nTRST上拉,而对TCK没有特别的建议。但在STM32F10xxx中, JTCK引脚带有下拉。

内嵌的上拉和下拉使芯片不再需要外加外部电阻利用串行接口并释放不用的调试脚作为普通I/O口为了利用串行调试接口来释放一些普通I/O口,用户软件必须在复位后设置SWJ_CFG=010,从而释放PA15, PB3和PB4用做普通I/O口。这点可以记住因为在平常我也忘记这了。