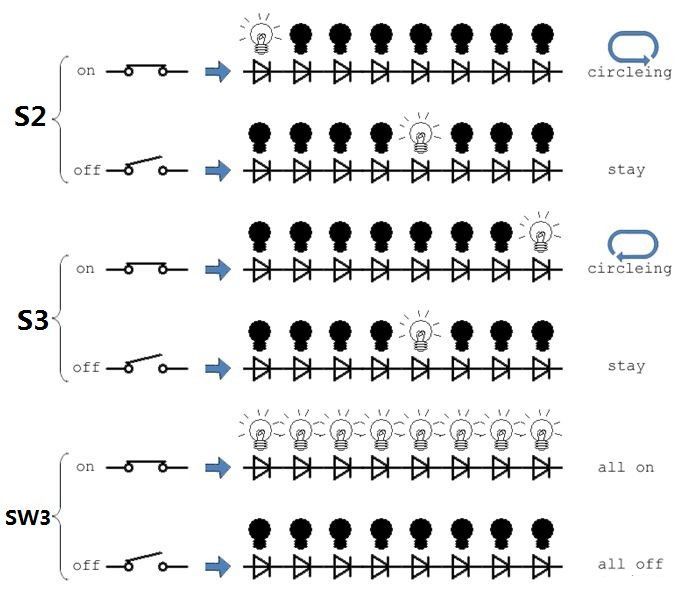

本实例使用一个拨码开关和2个独立按键控制流水灯的各种不同变化模式。模式流水灯功能示意如图8.15所示。

图8.15 模式流水灯功能示意图

这里我们需要注意,当拨码开关SW3处于OFF时,LED停止不动,只有一个LED处于点亮,并且点亮的LED不会变化;而SW3处于ON状态时,流水灯处于流动状态。按键S1被按下后,LED流动方向是从上到下(D9到D2方向);导航按键S2被按下后,LED流动方向是从下到上(D2到D9)。

本实例代码虽然比之前几个实例都要长,但是我们可以把它们解析来看,其实也不复杂。首先,接口部分代码如下,除了时钟和复位信号,还有拨码开关switch[0]、2个独立按键key_v[1]和key_v[0]、8个LED指示灯信号led[7:0]。

module cy4(

input ext_clk_25m, //外部输入25MHz时钟信号

input ext_rst_n, //外部输入复位信号,低电平有效

input[0:0] switch, //拨码开关SW3输入,ON -- 低电平;OFF-- 高电平

input[1:0] key_v,//S1/S2两个按键输入,未按下为高电平,按下后为低电平

output reg[7:0] led //8个LED指示灯接口

);

//-------------------------------------

//按键抖动判断逻辑

wire key; //所有按键值相与的结果,用于按键触发判断

reg[3:0] keyr;//按键值key的缓存寄存器

assign key = key_v[0] & key_v[1];

always @(posedge ext_clk_25m or negedge ext_rst_n)

if (!ext_rst_n) keyr <=4'b1111;

else keyr <= {keyr[2:0],key};

wire key_neg = ~keyr[2] & keyr[3]; //有按键被按下

wire key_pos = keyr[2] & ~keyr[3]; //有按键被释放

//-------------------------------------

//定时计数逻辑,用于对按键的消抖判断

reg[19:0]cnt;

always @ (posedge ext_clk_25m or negedge ext_rst_n)

if (!ext_rst_n) cnt <= 20'd0;

else if(key_pos || key_neg) cnt<=20'd0;

else if(cnt < 20'd999_999) cnt<= cnt + 1'b1;

else cnt <= 20'd0;

reg[1:0] key_value[1:0];

always @(posedge ext_clk_25m or negedge ext_rst_n)

if (!ext_rst_n) begin

key_value[0] <= 2'b11;

key_value[1] <= 2'b11;

end

else if(cnt == 20'd999_999) begin//定时键值采集

key_value[0] <= key_v;

key_value[1] <=key_value[0];

end

wire[1:0] key_press = key_value[1] & ~key_value[0]; //消抖后按键值变化标志位

有了按键值标志信号key_press,我们接下来就用它来控制LED流水灯的2个指示信号,即LED流水灯工作使能信号led_en和LED流水灯方向控制信号led_dir。

//------------------------------------

//流水灯开启、停止和流动方向控制开关、按键值采集

reg led_en; //LED流水灯工作使能信号,高电平有效

reg led_dir; //LED流水灯方向控制信号,1--从高到低流动,0--从低到高流动

always @ (posedge ext_clk_25m or negedge ext_rst_n)

if(!ext_rst_n) begin

led_en <= 1'b0;

led_dir <= 1'b0;

end

else begin

//流水灯开启/停止控制

if(!switch[0]) led_en <= 1'b1;

else led_en <= 1'b0;

//流水灯方向控制

if(key_press[0]) led_dir <=1'b0;//从低到高流动

else if(key_press[1]) led_dir<= 1'b1; //从高到低流动

else ;

end

最后两个always语句,前者对24bit计数器delay做循环计数,用于产生LED流水灯变化的切换频率;后者则根据led_en和led_dir信号控制8个LED流水灯实现最终的工作与否以及流动方向控制。

//------------------------------------

//LED流水灯变化延时计数器

reg[23:0] delay;

always @ (posedge ext_clk_25m or negedge ext_rst_n)

if(!ext_rst_n) delay <= 24'd0;

else delay <= delay+1'b1;

//-------------------------------------

//流水灯开启、停止和流动切换控制

always @ (posedge ext_clk_25m or negedge ext_rst_n)

if(!ext_rst_n) led <=8'b1111_1110;

else if((delay == 24'h3fffff)&& led_en) begin

case (led_dir)

1'b0: led <={led[6:0],led[7]}; //从低到高流动

1'b1: led <={led[0],led[7:1]}; //从高到低流动

default: ;

endcase

end

else ;

endmodule