目前异构加速器的实现主要借助于专用集成电路(ASIC)、图形处理单元(GPU)、现场可编程门阵列(FPGA)等异构计算部件。在上述几种典型的异构体系结构中,基于FPGA和CGRA等可重构体系结构的异构加速器具有以下两个优点:

第一,FPGA和CGRA等结构内部包含大量可配置的逻辑电路,能够满足特定应用的高性能和低功耗的运行要求,从而获得较高的效能比。

第二,由于目前新型应用的种类多样、迭代速度快,而采用ASIC进行加速器设计的周期又比较长,与之相比,采用FPGA和CGRA等可重构体系结构能够快速实现原型系统,并能够根据应用和算法的迭代进行演化,具有良好的定制性和可重构特性。

近年来,在体系结构的顶级国际会议上,涌现了一批以可重构体系结构为基础的异构加速器工作,成为学术界的研究热点。与此同时,基于FPGA的加速器平台也成为工业界关注的关键技术之一,国际知名的公司如Intel、微软等都将可重构计算加速器作为构建下一代异构加速器的重要平台,将其广泛应用于数据中心和嵌入式设备中。

为了更好的回顾近年来的可重构计算加速器相关工作,报告将以最近的可重构计算加速器体系结构以及算法应用等高水平科研成果为基础,对国内外的相关研究热点和关注领域进行客观对比,对可重构计算加速器的优缺点和挑战进行了详细的分析和说明。由于计算机体系结构是国内外计算机领域发展差距较大的方向之一,报告将以可重构计算加速器为切入点,着重分析FPGA和可重构计算加速器等技术给国内体系结构研究人员带来的新机遇和挑战,展望加速器体系结构未来的发展趋势。报告中的相关内容希望能为我国计算机体系结构领域的研究提供参考。

国内外研究进展比较

作者对可重构计算加速器在国内外的研究进展进行客观对比。首先,统计了在可重构计算加速器领域国内外的研究工作(主要涉及在高水平会议和期刊上发表的相关工作)。其次,将围绕体系结构和算法应用两个层次的代表性工作进行重点分析。第三,围绕加速器的成熟度和解决方案等方面,对国际和国内的进展进行比较。通过上述分析,作者给出国内加速器研究存在的主要问题,旨在找到与国际顶尖水平的差距。

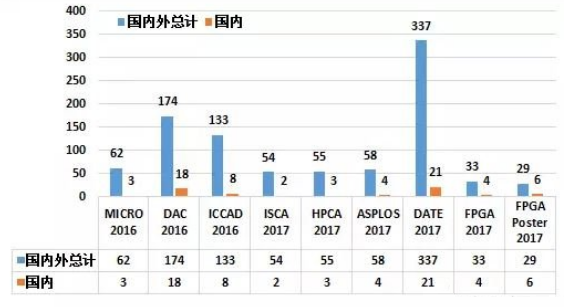

我们对计算机体系结构顶级会议收录论文情况进行了统计,这其中包括MICRO 2016,DAC 2016,ICCAD 2016,ISCA 2017,HPCA 2017,ASPLOS 2017,DATE 2017,FPGA 2017等有代表性的国际会议。具体情况如下所示:

图1 国内外相关工作在体系结构顶会中的录用情况

从图中我们可以看出,国内相关研究工作出现在体系结构顶级会议上的频率较之从前已经在逐步提升,并且在工作质量方面也取得了长足进步。其中,中科院计算所陈云霁研究院团队提出的神经网络指令集Cambricon还获得了ISCA 2016的最高评分。但是与此同时,目前国内在体系结构领域的研究点较为集中,国外在这一领域的研究面更为广泛,在系统功耗、并行性、可靠性、安全性等基础研究,以及新型存储系统、云计算、大型数据中心和加速器等方面均有丰富的研究成果。国内目前的研究主要集中在大数据应用以及专用加速器设计方面,缺乏在体系结构层面上的基础性的研究。因此,我们需要认清体系结构基础学科研究对于上层科研的重要性,加大在基础领域的研究投入和人才培养力度。

从体系结构整体角度来看,在加速器设计方面,国外主要侧重于加速器架构、新型材料、编程框架以及特定应用等方面研究,涌现出了一批优秀的研究成果,并且形成了一整套完备的开发体系,比如基于新型材料的PipeLayer加速器、基于ASIC的CNN加速器—Eyeriss 和基于FPGA的框架¬—DNNWeaver等。在国内加速器的通用性和灵活性上面关注的不多,而经常集中在研究单一特定的算法上的加速效果上。中科院和寒武纪公司在此方面的工作较为优秀,提出了基于ASIC的神经网络加速器—DianNao系列以及稀疏网络的深度学习加速器—Cambricon-X等。我们需要意识到国内外在此领域的差距,可重构计算加速器是软件和硬件相互配合的产物,单一的研究软件或者硬件并不能达到很好的效果,国内主要是侧重于单一应用的加速效果的研究,没有形成完备的研究体系。

对于计算机体系结构而言,它是软硬件系统的总称,涉及面广、结构复杂。目前,众多计算密集型和数据密集型的任务对计算机体系结构提出了更高的要求,为了提升性能并降低功耗满足日益增长的需求,使得其结构进一步复杂,给科研人员带来了更大的挑战,同时也带来了更多的机遇。

发展趋势与展望

自从计算机诞生的时候开始,国内外研究者们即注意到计算机体系结构对计算机系统的性能的影响。事实上,从来不存在某种特定的计算机体系结构对所有的应用、任务来说都能得到最优的性能,例如,深度学习等领域的应用并行度较高,最适合处理该类任务的架构是多核并行架构;另一方面,有一些科学计算相关的任务,其本身无法并行,因此最适合的架构是单核架构,并且需要极大的提升单核的性能。正是由于不同的计算任务有着适合自身的计算机架构,因此上世纪60年代Gerald Estrin提出了可重构计算(Reconfigurable CompuTIng)的概念。可重构计算包括作为中央控制单元的CPU,众多可重构的计算单元(Reconfigurable Processing Unit),这些可重构计算单元由中央处理器CPU控制,在执行相应的任务(如科学计算、图像识别、模式识别等)的时候,可重构计算单元配置成最优的架构(也即硬件编程)。Reiner Hartenstein等在文献[202]中指出,可重构计算使得计算单元的时钟频率远低于CPU,但是综合计算能力却高于CPU数倍,而且功耗也低于CPU。可重构计算加速器有着种种优点,但是也存在这自身的一些缺点,如重构开销大,编程复杂度高等。本报告对可重构计算加速器的优缺点进行总结,并对可重构计算技术应用前景与趋势进行展望。

可重构计算加速器的优点

1. 低功耗和高性能

正如前面所述,低功耗和高性能是可重构计算加速器最明显的优势之一,可重构计算使得计算单元的时钟频率远低于通用CPU,但是计算能力却是通用CPU的数倍,并且极大的降低了系统的功耗。对于高性能优势方面,文献[203]证明在一块66MHz的FPGA芯片XC2V6000上实现密钥长度为270位的椭圆曲线密码算法的点积操作只需要0.36ms;而在两个2.6GHz的Intel Xeon计算机上采用优化的软件实现该算法则需要196.71ms。FPGA可重构计算加速器的性能要高出通用CPU 540多倍,同时时钟频率降低了40倍。此外,Xilinx FPGA硬件可以非常高效地实现各种计算,例如,实现相同的性能,使用FPGA加速器仅需要CPU服务器所占空间的1/12, 功耗为CPU服务器的1/12,而成本也仅为CPU服务器的1/10[204]。

2. 安全性

随着大数据时代的到来,数据扮演的角色越来越重要,计算机作为数据的载体,其安全性变得至关重要。目前,人们提及计算机安全性问题,第一反应是各种杀毒软件保护着电脑。其实,软件只能扮演被动的防御者,无法消除安全隐患。但是从体系结构硬件层面能够更好的提升安全性,甚至杜绝安全隐患。

3. 灵活性

可重构计算加速器天生的可重构特性使其对于复杂的计算场景仍然有效,例如多功能硬件加速器可以应对频繁的设计变更。在面对用户需求发生改变的时候,只需要采用特定的重构技术对加速器进行重构即可满足用户的需求,因此灵活性也是可重构计算加速器的一大亮点。随着大数据和云计算的发展,可重构计算加速器的灵活性表现的更为淋漓尽致,如2016年11月中旬FPGA巨头Xilinx在超算大会上发布的可重构加速栈(Reconfigurable AcceleraTIon Stack)旨在加速可重构计算生态建设。在可重构加速栈中,Xilinx提供了目前流行应用框架的整合,其中包括Caffe(深度学习框架)、FFMPEG(图像视频处理)以及SQL(数据库)。在此架构之上,云端服务器的程序员无需使用硬件描述语言就可以配置和应用加速栈中的模块,此外Xilinx还提供了各种库,通过在程序中调用这些库可以更加灵活的应用FPGA来进行加速。

4. 并行性

实际经验已经表明流水线带来性能的提高,高并行性能够有效的加快程序运行速度。随着流水线深度的增加,造成结构复杂,硬件开销较大,并且对应用或者程序本身也提出了更高的并行性要求。如果贸然地并行执行每个程序会造成系统开销剧增,得不偿失。随着可并行处理的应用越来越多,对于并行性的需求会剧增,因此对于体系结构中并行性的研究具有光明的未来。

5. 低成本

随着芯片制造逐步向纳米工艺逼近,FPGA 的优势越来越明显,尤其是通过重构多个软核,可以在单片上实现多个指令集的处理器,根据现场计算任务的划分,实时实现不同的处理器功能,达到一次芯片设计,多个功能实现,从而大幅度降低芯片设计和制造的 NRE(Non-Recurring Expenses ,一次性工程费用)成本,通过广阔的市场分摊成本,获得总体上的性能/价格优势,同时将软件实现(通用处理器)的灵活性和硬件实现(ASIC)的高性能优点合二为一[205]。

可重构计算加速器的缺点

1. 可重构开销明显

在可重构计算加速器设计与实现的过程当中,通常需要对FPGA进行配置,该过程包括综合以及布局布线,然而综合、布局布线操作所耗费的时间长达几十分钟甚至数小时,具体时长决定于加速器的复杂程度。重构按照重构的时机不同可分为静态可重构和动态可重构。静态可重构又称为编译时重构,是指在开始执行任务之前,一次性将可重构硬件配置为系统所需的某个或者某几个功能,并且这些配置好的功能在整个任务的执行期间不会被改变,直至整个任务执行结束,这些可重构硬件才能重新配置去完成其他的任务;而动态可重构又称为运行时重构,其是指在任务执行的过程中随时重新配置可重构硬件,运行时重构多为部分重构,通常采用上下文配置模式。实现动态可重构系统的关键是重新配置硬件必须尽可能的高效的和尽可能的快,如果配置延迟太大,可能会影响到计算的连续性,这样会使得重构的开销抵消可重构硬件加速带来的加速效果。例如,在 DISC II 系统中,25~71%的执行时间花费在重构上;在 UCLAATR 中重构时间达到了 98.5%。

2. 编程复杂度较高

尽管可重构计算架构概念很早之前就已经提出,并且已经有许多较为成熟的工作,但是可重构计算在当年并没有得到普及。其原因有两点:(1)从可重构计算提出到21世纪初近40年的时间正是摩尔定律发展的黄金时期,工艺每一年半更新一次,因此架构上更新带来的性能增强不如工艺更新来的直接;(2)传统的CPU上的编程使用的是高级抽象编程语言(如Java、C/C++等),并且这种编程体系已经成熟,然而可重构计算则需要对硬件进行编程,通常使用硬件编程语言(如Verilog、VHDL等),这些语言对于程序员来说需要大量的时间才能掌握。

展望

在以往若干年的学术界和工业界的研究当中,大多采用通用CPU来处理不同的类型的计算任务,随着上层应用的不断更迭,CPU的频率和性能也在不断的上升,用户为了使用方便,更倾向于选择已经较为成熟的CPU来处理不同的任务。但是近年来一方面随着摩尔定律的失效,另一方面大数据对计算机的运算需求的迅猛增加,使得通用处理器的发展遇到瓶颈,导致一味的提升通用处理器的频率和性能并不能很好的满足用户的需求,因此国内外研究学者将眼光纷纷投向专用加速器的设计,旨在设计适合处理不同任务的专用加速器来满足用户的需求,CPU从原来巨量且复杂的工作中抽离出来,此时CPU只需要将计算任务分发给对应的加速器来完成即可。

可重构计算技术已经广泛应用在科学计算、国防军事、航空航天等诸多领域,用于实现如目标匹配、大数值运算、数据挖掘、模型仿真等功能,都取得了非常好的效果。目前可重构计算技术的应用也在逐渐向民用领域扩展,在汽车电子、网络设备等领域已经有产品出现。对可重构计算技术的研究这些年也是方兴未艾。从可重构计算技术方面的国际会议(如ReConFig、ERSA、RAW、ARC等)的主题可以看出,对可重构计算技术的研究主要集中在可重构计算体系结构、可重构计算应用、可重构计算工具、可重构计算教育、可重构计算性能测试等方面。

随着大数据与人工智能的发展,我国国内目前普遍存在着软件方面的人才相对较多,而硬件方面的人才比较匮乏的现象。这主要是由于要想精通底层的硬件结构,需要对计算机的组成原理和运作方式有着充分的了解与掌握,不幸的是这部分内容也是计算机领域的难点。同时由于可重构计算正是基于可重构硬件平台展开的计算机研究,因此这也造成可重构计算成为当前研究的一大难点。在前面充分对国内外可重构计算调研的基础上,我们总结以下三个国内可以在可重构计算领域发挥自身特长的研究想法,仅供大家参考。

(1)对可重构计算的研究离不开可重构计算的专业性人才,但是目前从国内情况来看,对可重构计算领域的人才培养力度还远远不够,只有少数一些国内的高校配备了相关的培养模式和条件。国内的可重构计算方向要想追赶甚至超越国外的相关研究水平,我们就需要建立合理、完善的可重构计算领域的人才培养模式,吸引更多的年轻有活力的研究学者或者研究团队来为可重构计算添砖加瓦;

(2)正如前面所述,要想可重构计算相关的研究有着长足有力的发展,就必须有工业界相关的可重构计算的研究平台进行支撑,然而这块国内做的也是不够,目前我们所用的硬件设备和编程工具基本上都是由国外的开发商巨头开发和生产,如Xilinx、Altera等。因此,我们也需要有国产的可重构硬件和自动编程工具对我国的可重构计算的研究做强有力的支撑;

(3)目前大多数可重构计算相关研究工作是基于某些特定应用展开可重构计算加速器的研究,如基于神经网络的加速器、基于图计算的加速器和数据挖掘算法加速器等。如何挖掘更多的新型的大数据应用和设计更具有针对性的可重构计算架构来加速应用也将是未来的研究热点之一。

总的来说,国内在可重构计算领域也有了飞速的发展,其中具有代表性的是国内一些著名学府和研究所的标志性工作。展望未来,集高性能、高灵活性、低功耗、低成本、高安全性和高并行性等优点于一身的可重构计算必将获得更大的发展和更广的应用。