摘要:本文设计实现了一款基于FPGA的PCM-FM遥测中频接收机,在FPGA中实现遥测信号解调、位同步、帧同步等功能,系统码速率、帧长、帧同步码可灵活设置。接收机硬件结构简单,主要包括FPGA、ADC、电源转换芯片、USB接口芯片等常用器件,可单板实现,达到低成本、小型化设计要求。性能测试表明,中频接收机满足设计指标要求,目前该接收机已服务于多个项目。

PCM-FM遥测系统[1]在航空、航天等领域得到广泛应用,国内外遥测厂家均致力于高码率、功能可扩展的遥测产品设计,多功能、通用化、小型化遥测接收系统应用需求越来越迫切,更小、更快、更灵活成为遥测接收技术的又一发展方向。随着数字技术的不断发展,尤其是FPGA技术的发展,遥测中频接收机小型化设计得以实现。本文设计了一款基于FPGA的PCM-FM遥测中频接收机,实现70MHz中频输入PCM-FM遥测信号的下变频、载波跟踪、解调、位同步、帧同步,并最终通过USB接口将数据传给计算机用以数据的存储及分析,接收机码速率、字长、帧长、帧同步码等均可由上位机软件通过USB接口进行设置,所有处理均在FPGA中完成,硬件电路仅由FPGA、AD、电源芯片、晶振等构成,可单板实现,达到小型化设计目的。

1 系统组成与工作原理

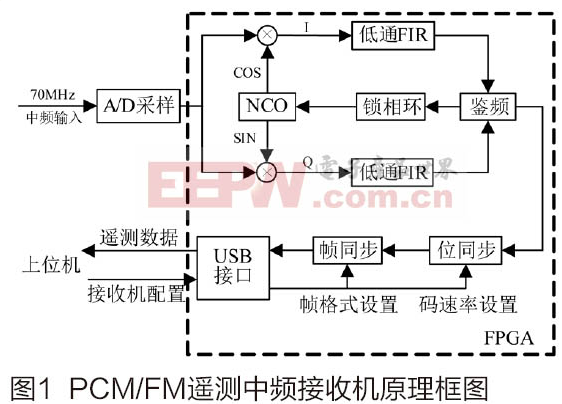

本文设计的PCM/FM遥测中频接收机原理框图如图1所示。

由图1可以看出,PCM/FM遥测中频接收机主要包括A/D采样、数字下变频、鉴频、位同步、帧同步及USB接口等功能模块。70MHz中频输入信号经40MHz带通采样送入FPGA进行处理,在FPGA中产生两路正交信号对A/D采样信号进行数字正交下变频生成基带I、Q信号,I、Q信号分别进行低通滤波后送入鉴频模块,通过叉积鉴频完成解调得到PCM码流,按上位机事先设置的码速率、帧同步码、帧长、时间码等,依次完成PCM码流的位同步、帧同步、时间码合并,最后通过USB接口送入上位机进行遥测数据的存贮和处理。

2 系统详细设计

2.1 数字下变频与FM解调

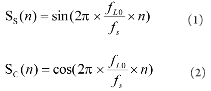

数字下变频与FM解调模块主要包括数控振荡器(NCO)、鉴频器、环路滤波器的设计,数字控制振荡器(NCO)是数字下变频器(DDC)的重要组成部分,它的作用是产生正弦和余弦信号。正、余弦信号如(1)、(2)式所示:

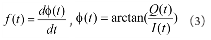

式中,fL0为NCO频率;fs为输入信号的采样频率。由于设计采用带通采样,信号频谱发生搬移。当fs=40MHz时,经过AD采样后,在10MHz、30MHz、70MHz等中心频率上都有所需的有用信号,本设计选择对中心频率为10MHz的有用信号进行混频,此时,fL0为10MHz。在FPGA实现时,采用查表法产生正、余弦信号,建立两个ROM表分别存储0º~90º的正、余弦量化值,通过频率控制字累加值的高两位判断当前的正、余弦值处于哪个象限,对查表输出值进行相应处理,最终得到正、余弦信号[2]。余弦、正弦信号分别与AD采样输入混频得到I、Q基带信号,经低通FIR滤波器滤波后送入数字鉴频器[3]。假设瞬时频率为f(t),瞬时相位为 ,同相分量为I(t),正交分量为Q(t),由:

,同相分量为I(t),正交分量为Q(t),由:

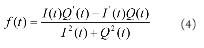

得到:

对应的数字域表达式为:

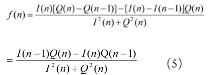

数字鉴频模块的实现框图见图2,鉴频输出即为FM解调得到的PCM码流

2.2 载波跟踪设计

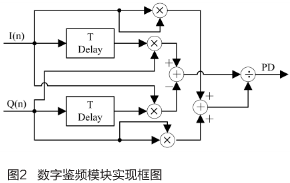

在高动态应用环境下,遥测接收机需具备抗多普勒频偏的能力,本设计中,鉴频输出经过一阶锁频环得到频率修正值并反馈给NCO,锁频环结构框图见图3。指标要求中频接收机抗多普勒频偏能力为250kHz,所以在实现时,对超出250kHz的频偏按250kHz进行处理。

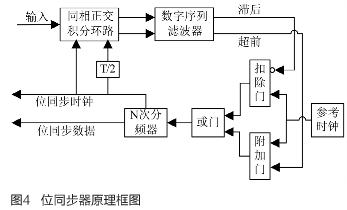

2.3位同步设计

设计采用直接位同步法中的数字锁相环方法实现位同步器设计[4]。在设计中利用数字锁相环来提取位同步信号:在接收端利用鉴相器比较接收码元和本地同步信号的相位,若两者相位不一致(超前或者滞后),鉴相器产生误差信号调整本地同步信号的相位,直至获得准确的位同步信息。位同步器主要由参考频率生成、同相正交积分环路、数字序列滤波器、分频器等几部分组成,其原理如图4所示。

本设计参考时钟为码速率的16倍,通过上位机设置接收机码速率时,参考时钟频率也相应得到设置,参考时钟的精度直接影响位同步器性能,因此,生成高质量的参考时钟是基本前提。在FPGA中采用查表法产生位同步参考时钟,原理与NCO生成一致,不再赘述,区别仅在于只取输出的符号位。

2.4帧同步设计

位同步输出经过串/并转换后,与本地帧同步码(由上位机设置)进行同或后全加,然后与门限值Nt进行比较,大于门限值表示接收到帧同步码。三态逻辑电路保证帧同步器在三个固定模式(搜索、校核、锁定)上工作[5]。在搜索态,不使用窗口,符合相关器输出即认为是帧同步码。一旦接收到帧同步码,转入校核态,位/字计数器、字/帧计数器复位并开始计数,这个过程一直持续到字/帧计数器达到预定的字/帧数。以预期检测位为中心产生窗口脉冲,利用帧同步码的周期性,下一个检测位应落在窗口脉冲宽度内,三态逻辑产生帧标志脉冲。若在窗口范围内,没有检测到帧同步码,认为是虚警,则从校核态返回到搜索态。在校核态,连续通过预定的校核帧数A,则帧同步器进入锁定态。在锁定态下,若帧同步码发生漏检或数据错误,帧标志脉冲由本地产生,以避免由于帧同步码的漏检而造成的数据丢失。连续漏检超过预定的保护帧数B,返回搜索态,否则保持在锁定态。

2.5 硬件设计

接收机以FPGA为中心,外围为晶振、电源模块、A/D转换电路和USB接口电路。

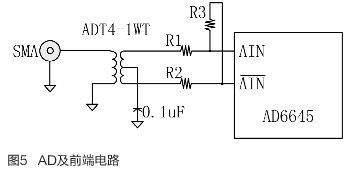

AD转换设计采用AD6645,AD6645是采用CMOS工艺的14位模数转换器,最高采样率为105MSPS,在中频为70MHz时的SNR为73.5dB,SFDR为89dBc,模拟带宽达200MHz[6]。AD模拟输入端为差分输入,通过阻抗比4:1的变压器进行交流耦合,电路原理图见图5。图中R1=R2=24.9Ω,R3=178Ω,输入端匹配阻抗为50Ω。AD时钟管脚与FPGA相连,采样频率由FPGA控制,本设计采样频率为40HMz。

FPGA选用Xilinx Spartan-6系列XC6SLX100工业级FPGA芯片。该芯片采用45nm工艺,专为低成本与低功耗而精心优化,集成了丰富的逻辑资源,接口可选择使用1.2V、1.5V、1.8V、2.5V或3.3V多种标准,便于与其它电路接口[7]。XC6SLX100 FPGA的配置文件大小为26,543,264bits,配置芯片选用XCF32P,采用BASIC Master Serial 配置模式,配置时钟由FPGA内部提供,配置速率22MHz。

遥测中频接收机与上位机之间采用USB接口,接口芯片选用CY7C68013,FPGA与CY7C68013间采用SlaveFIFO通信模式。

3 测试结果

搭建测试平台,遥测接收系统由射频接收机、本文设计的中频接收机、上位机等组成。中频接收机测试结果:最大多普勒频偏250kHz、码速率100kbps~5Mbps可调、抗连续连0或连1可达128位、帧长与帧同步码可灵活设置。结果表明满足设计指标要求。

4 结论

本文设计了一款基于FPGA的PCM/FM 遥测中频接收机,码速率、帧长、帧同步码等可灵活设置,硬件结构简单,可单板实现,达到小型化、低成本设计目的。目前,该接收机已服务于多个项目,性能稳定可靠。

参考文献:

[1] 李英丽,刘春亭.空空导弹遥测系统设计[M].北京:国防工业出版社,2006

[2] Uwe Meyer-Baese.数字信号处理的FPGA实现[M].北京:清华大学出版社,2002

[3] Miao G J.Signal processing in digitai communications [M].Artech House Inc,2007

[4] 樊昌信,詹道庸,徐炳祥等.通信原理(第四版)[M].北京:国防工业出版社,2001

[5] 夏利利,刘冰,周江等.PCM遥测帧同步技术性能分析[J].电讯技术,2014, 54(6):803-807

[6] AD6645 Data Sheet,Analog Device Inc,2002

[7] Xilinx Inc.Data Sheet,Spartan-6 Family Overiew,2010