一、PCB走线中途容性负载反射

很多时候,PCB走线中途会经过过孔、测试点焊盘、短的stub线等,都存在寄生电容,必然对信号造成影响。走线中途的电容对信号的影响要从发射端和接受端两个方面分析,对起点和终点都有影响。

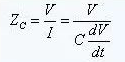

首先按看一下对信号发射端的影响。当一个快速上升的阶跃信号到达电容时,电容快速充电,充电电流和信号电压上升快慢有关,充电电流公式为:I=C*dV/dt。电容量越大,充电电流越大,信号上升时间越快,dt越小,同样使充电电流越大。

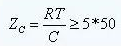

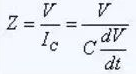

我们知道,信号的反射与信号感受到的阻抗变化有关,因此为了分析,我们看一下,电容引起的阻抗变化。在电容开始充电的初期,阻抗表示为:

这里dV实际上是阶跃信号电压变化,dt为信号上升时间,电容阻抗公式变为:

从这个公式中,我们可以得到一个很重要的信息,当阶跃信号施加到电容两端的初期,电容的阻抗与信号上升时间和本身的电容量有关。

通常在电容充电初期,阻抗很小,小于走线的特性阻抗。信号在电容处发生负反射,这个负电压信号和原信号叠加,使得发射端的信号产生下冲,引起发射端信号的非单调性。

对于接收端,信号到达接收端后,发生正反射,反射回来的信号到达电容位置,那个样发生负反射,反射回接收端的负反射电压同样使接收端信号产生下冲。

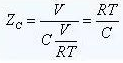

为了使反射噪声小于电压摆幅的5%(这种情况对信号影响可以容忍),阻抗变化必须小于10%。那么电容阻抗应该控制在多少?电容的阻抗表现为一个并联阻抗,我们可以用并联阻抗公式和反射系数公式来确定它的范围。对于这种并联阻抗,我们希望电容阻抗越大越好。假设电容阻抗是PCB走线特性阻抗的k倍,根据并联阻抗公式得到电容处信号感受到的阻抗为:

阻抗变化率为: ,即

,即 ,也就是说,根据这种理想的计算,电容的阻抗至少要是PCB特性阻抗的9倍以上。实际上,随着电容的充电,电容的阻抗不断增加,并不是一直保持最低阻抗,另外,每一个器件还会有寄生电感,使阻抗增加。因此这个9倍限制可以放宽。

,也就是说,根据这种理想的计算,电容的阻抗至少要是PCB特性阻抗的9倍以上。实际上,随着电容的充电,电容的阻抗不断增加,并不是一直保持最低阻抗,另外,每一个器件还会有寄生电感,使阻抗增加。因此这个9倍限制可以放宽。

在下边的讨论中假设这个限制是5倍。

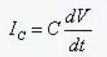

有了阻抗的指标,我们就可以确定能容忍多大的电容量。电路板上50欧姆特性阻抗很常见,我就用50欧姆来计算。

得出:

即在这种情况下,如果信号上升时间为1ns,那么电容量要小于4皮法。反之,如果电容量为4皮法,则信号上升时间最快为1ns,如果信号上升时间为0.5ns,这个4皮法的电容就会产生问题。

这里的计算只不过是为了说明电容的影响,实际电路中情况十分复杂,需要考虑的因素更多,因此这里计算是否精确没有实际意义。关键是要通过这种计算理解电容是如何影响信号的。我们对电路板上每一个因素的影响都有一个感性认识后,就能为设计提供必要的指导,出现问题就知道如何去分析。精确的评估需要用软件来仿真。

总结:1. PCB走线中途容性负载使发射端信号产生下冲,接收端信号也会产生下冲。2.能容忍的电容量和信号上升时间有关,信号上升时间越快,能容忍的电容量越小。

二、接收端容性负载的反射

信号的接收端可能是集成芯片的一个引脚,也可能是其他元器件。不论接收端是什么,实际的器件的输入端必然存在寄生电容,接受信号的芯片引脚和相邻引脚之间有一定的寄生电容,和引脚相连的芯片内部的布线也会存在寄生电容,另外引脚和信号返回路径之间也会存在寄生电容。

好复杂,这么多寄生电容!其实很简单,想想电容是什么?两个金属板,中间是某种绝缘介质。这个定义中并没有说两个金属板是什么形状的,芯片两个相邻引脚也可以看做是电容的两个金属板,中间介质是空气,

不就是一个电容么。芯片引脚和PCB板内层的电源或地平面也是一对金属板,中间介质是PCB板的板材,常见的是FR4材料,也是一个电容。呵呵,搞来搞去,还是回到了最基础的部分。高手不要笑,太简单了。不过确实很多人看到寄生电容就感到有点晕,理解不透,所以在这里啰嗦一下。

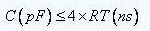

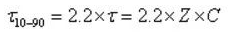

回到正题,下面研究一下信号终端的电容有什么影响。将模型简化,用一个分立电容元件代替所有寄生电容,如图1所示。

我们考察B点电容的阻抗情况。电容的电流为:

随着电容的充电,电压变化率逐渐减小(电路原理中的瞬态过程),电容的充电电流也不断减小。即电容的充电电流是随时间变化的。

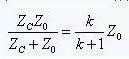

电容的阻抗为:

因此电容所表现出来的阻抗随时间变化,不是恒定的。正是这种阻抗的变化特性决定了电容对信号影响的特殊性。如果信号上升时间小于电容的充电时间,最初电容两端的电压迅速上升,这时阻抗很小。随着电容充电,电压变化率下降,充电电流减小,表现为阻抗明显增大。充电时间无穷大时,电容相当于开路,阻抗无穷大。

阻抗的变化必然影响信号的反射。在充电的开始一段时间,阻抗很小,小于传输线的特性阻抗,将发生负反射,反射回源端A点的信号将产生下冲。随着电容阻抗的增加,反射逐渐过渡到正反射,A点的信号经过一个下冲会逐渐升高,最终达到开路电压。

因此电容负载使源端信号产生局部电压凹陷。精确波形和传输线的特性阻抗、电容量、信号上升时间有关。

对于接收端,很明显,就是一个RC充电电路,不是很严谨,但是和实际情况非常相似。电容两端电压,即B点电压随RC充电电路的时间常数呈指数增加(基本电路原理)。因此电容对接收端信号上升时间产生影响。

RC充电电路的时间常数为

这是B点电压上升到电压终值的 即37%所需的时间。B点电压10%~90%上升时间为

即37%所需的时间。B点电压10%~90%上升时间为

如果传输线特性阻抗为50欧姆,电容量10pF,则10~90充电时间为1.1ns。如果信号上升时间小于1.1ns,那么B点电压上升时间主要由电容充电时间决定。如果信号上升时间大于1.1ns,末端电容器作用是使上升时间进一步延长,增加约1.1ns(实际应比这个值小)。图2显示了终端电容负载对驱动端和接受端产生影响的示意图,放在这里,让大家能有个感性的认识。

图2

图2

至于信号上升时间增加的精确值是多少,对于电路设计来说没必要,只要定性的分析,有个大致的估算就可以了。因为计算再精确也没实际意义,电路板的参数也不精确!对于设计者来说,定性分析并了解影响,大致估算出影响在那个量级,能给电路设计提供指导就可以了,其他的事软件来做吧。

举个例子,如果信号上升时间1ns,电容使信号上升时间增加远小于1ns,比如0.2 ns,那么这么一点点增加可能不会有什么影响。如果电容造成的上升时间增加很多,那可能就会对电路时序产生影响。那么多少算很多?看看电路的时序余量吧,这涉及到电路的时序分析和时序设计。

总之接收端电容负载的影响有两点:

1、使源端(驱动端)信号产生局部电压凹陷。2、接收端信号上升时间延长。

在电路设计中这两点都要考虑。

三、PCB走线宽度变化产生的反射

在进行PCB布线时,经常会发生这样的情况:走线通过某一区域时,由于该区域布线空间有限,不得不使用更细的线条,通过这一区域后,线条再恢复原来的宽度。走线宽度变化会引起阻抗变化,因此发生反射,对信号产生影响。那么什么情况下可以忽略这一影响,又在什么情况下我们必须考虑它的影响?

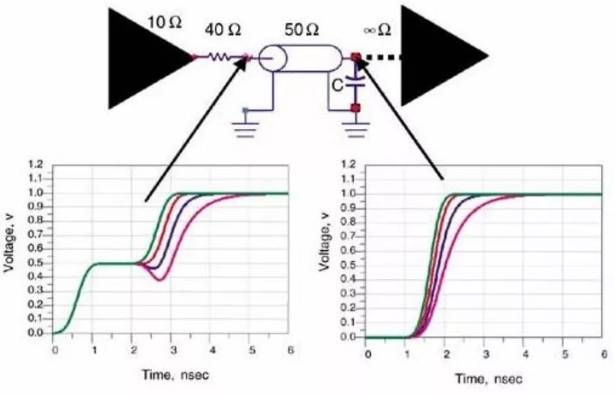

有三个因素和这一影响有关:阻抗变化的大小、信号上升时间、窄线条上信号的时延。首先讨论阻抗变化的大小。很多电路的设计要求反射噪声小于电压摆幅的5%(这和信号上的噪声预算有关),根据反射系数公式:

以计算出阻抗大致的变化率要求为: 你可能知道,电路板上阻抗的典型指标为+/-10%,根本原因就在这。

你可能知道,电路板上阻抗的典型指标为+/-10%,根本原因就在这。

如果阻抗变化只发生一次,例如线宽从8mil变到6mil后,一直保持6mil宽度这种情况,要达到突变处信号反射噪声不超过电压摆幅的5%这一噪声预算要求,阻抗变化必须小于10%。这有时很难做到,以 FR4板材上微带线的情况为例,我们计算一下。

如果线宽8mil,线条和参考平面之间的厚度为4mil,特性阻抗为46.5欧姆。线宽变化到6mil后特性阻抗变成54.2欧姆,阻抗变化率达到了20%。反射信号的幅度必然超标。至于对信号造成多大影响,还和信号上升时间和驱动端到反射点处信号的时延有关。但至少这是一个潜在的问题点。幸运的是这时可以通过阻抗匹配端接解决问题。

如果阻抗变化发生两次,例如线宽从8mil变到6mil后,拉出2cm后又变回8mil。那么在2cm长6mil宽线条的两个端点处都会发生反射,一次是阻抗变大,发生正反射,接着阻抗变小,发生负反射。如果两次反射间隔时间足够短,两次反射就有可能相互抵消,从而减小影响。

假设传输信号为1V,第一次正反射有0.2V被反射,1.2V继续向前传输,第二次反射有 -0.2*1.2 = 0.24v被反射回。再假设6mil线长度极短,两次反射几乎同时发生,那么总的反射电压只有0.04V,小于5%这一噪声预算要求。因此,这种反射是否影响信号,有多大影响,和阻抗变化处的时延以及信号上升时间有关。

研究及实验表明,只要阻抗变化处的时延小于信号上升时间的20%,反射信号就不会造成问题。如果信号上升时间为1ns,那么阻抗变化处的时延小于0.2ns对应1.2英寸,反射就不会产生问题。也就是说,对于本例情况,6mil宽走线的长度只要小于3cm就不会有问题。

当PCB走线线宽发生变化时,要根据实际情况仔细分析,是否造成影响。需要关注的参数由三个:阻抗变化有多大、信号上升时间是多少、线宽变化的颈状部分有多长。根据上面的方法大致估算一下,适当留出一定的余量。如果可能的话,尽量让减小颈状部分长度。

需要指出的是,实际的PCB加工中,参数不可能像理论中那样精确,理论能对我们的设计提供指导,但不能照搬照抄,不能教条,毕竟这是一门实践的科学。估算出的值要根据实际情况做适当的修订,再应用到设计中。如果感觉经验不足,那就先保守点,然后在根据制造成本适当调整.

四、信号振铃是怎么产生的

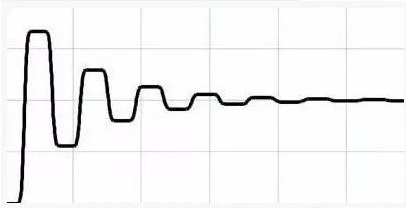

信号的反射可能会引起振铃现象,一个典型的信号振铃如图1所示。

图1

图1

那么信号振铃是怎么产生的呢?

前面讲过,如果信号传输过程中感受到阻抗的变化,就会发生信号的反射。这个信号可能是驱动端发出的信号,也可能是远端反射回来的反射信号。根据反射系数的公式,当信号感受到阻抗变小,就会发生负反射,反射的负电压会使信号产生下冲。

信号在驱动端和远端负载之间多次反射,其结果就是信号振铃。大多数芯片的输出阻抗都很低,如果输出阻抗小于PCB走线的特性阻抗,那么在没有源端端接的情况下,必然产生信号振铃。

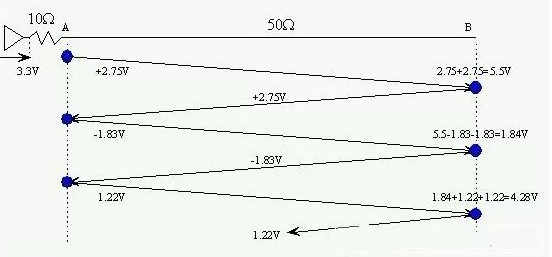

信号振铃的过程可以用反弹图来直观的解释。假设驱动端的输出阻抗是10欧姆,PCB走线的特性阻抗为50欧姆(可以通过改变PCB走线宽度,PCB走线和内层参考平面间介质厚度来调整),为了分析方便,假设远端开路,即远端阻抗无穷大。驱动端传输3.3V电压信号。我们跟着信号在这条传输线中跑一次,看看到底发生了什么?为分析方便,忽略传输线寄生电容和寄生电感的影响,只考虑阻性负载。图2为反射示意图。

图2

图2

第1次反射:信号从芯片内部发出,经过10欧姆输出阻抗和50欧姆PCB特性阻抗的分压,实际加到PCB走线上的信号为A点电压3.3*50/(10+50)=2.75V。传输到远端B点,由于B点开路,阻抗无穷大,反射系数为1,即信号全部反射,反射信号也是2.75V。此时B点测量电压是2.75+2.75=5.5V。

第2次反射:2.75V反射电压回到A点,阻抗由50欧姆变为10欧姆,发生负反射,A点反射电压为-1.83V,该电压到达B点,再次发生反射,反射电压-1.83V。此时B点测量电压为5.5-1.83-1.83=1.84V。

第3次反射:从B点反射回的-1.83V电压到达A点,再次发生负反射,反射电压为1.22V。该电压到达B点再次发生正反射,反射电压1.22V。此时B点测量电压为1.84+1.22+1.22=4.28V。

第4次反射:。。。。。。。。。第5次反射:。。。。。。。。。

如此循环,反射电压在A点和B点之间来回反弹,而引起B点电压不稳定。观察B点电压:5.5V->1.84V->4.28V->……,可见B点电压会有上下波动,这就是信号振铃。

信号振铃根本原因是负反射引起的,其罪魁祸首仍然是阻抗变化,又是阻抗!在研究信号完整性问题时,一定时时注意阻抗问题。

负载端信号振铃会严重干扰信号的接受,产生逻辑错误,必须减小或消除,因此对于长的传输线必须进行阻抗匹配端接。

五、信号反射

信号沿传输线向前传播时,每时每刻都会感受到一个瞬态阻抗,这个阻抗可能是传输线本身的,也可能是中途或末端其他元件的。对于信号来说,它不会区分到底是什么,信号所感受到的只有阻抗。如果信号感受到的阻抗是恒定的,那么他就会正常向前传播,只要感受到的阻抗发生变化,不论是什么引起的(可能是中途遇到的电阻,电容,电感,过孔,PCB转角,接插件),信号都会发生反射。

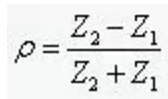

那么有多少被反射回传输线的起点?衡量信号反射量的重要指标是反射系数,表示反射电压和原传输信号电压的比值。反射系数定义为:

其中: 为变化前的阻抗,

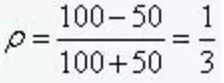

为变化前的阻抗, 为变化后的阻抗。假设PCB线条的特性阻抗为50欧姆,传输过程中遇到一个100欧姆的贴片电阻,暂时不考虑寄生电容电感的影响,把电阻看成理想的纯电阻,那么反射系数为:

为变化后的阻抗。假设PCB线条的特性阻抗为50欧姆,传输过程中遇到一个100欧姆的贴片电阻,暂时不考虑寄生电容电感的影响,把电阻看成理想的纯电阻,那么反射系数为: ,信号有1/3被反射回源端。如果传输信号的电压是3.3V电压,反射电压就是1.1V。

,信号有1/3被反射回源端。如果传输信号的电压是3.3V电压,反射电压就是1.1V。

纯电阻性负载的反射是研究反射现象的基础,阻性负载的变化无非是以下四种情况:阻抗增加有限值、减小有限值、开路(阻抗变为无穷大)、短路(阻抗突然变为0)。

阻抗增加有限值:反射电压上面的例子已经计算过了。这时,信号反射点处就会有两个电压成分,一部分是从源端传来的3.3V电压,另一部分是在反射电压1.1V,那么反射点处的电压为二者之和,即4.4V。

阻抗减小有限值:仍按上面的例子,PCB线条的特性阻抗为50欧姆,如果遇到的电阻是30欧姆,则反射系数为ρ=(30-50)/(30+50)=-0.25,反射系数为负值,说明反射电压为负电压,值3.3V*(-0.25V)=-0.825V,为此时反射点电压为3.3V+(-0.825V)=2.475V。

开路:开路相当于阻抗无穷大,反射系数按公式计算为1。即反射电压3.3V。反射点处电压为6.6V。可见,在这种极端情况下,反射点处电压翻倍了。

短路:短路时阻抗为0,电压一定为0。按公式计算反射系数为-1,说明反射电压为-3.3V,因此反射点电压为0。