随着科技的发展,.纠错码和差错控制技术在我们的生活里扮演了越来越重要的角色,其中卷积码由于其出色的纠错性能而得到了广泛使用。Viterbi译码算法是卷积码的一种概率译码算法,自Viterbi算法提出以来,无论在理论上还是在实践上都得到了极其迅速的发展。本论文对符合DVB一T标准的维特比译码器进行了研究,它是整个DVB一T接收机内码解码的核心部分,有重要的研究价值。

本文在综合了国内外近年来在维特比译码算法以及相关实现技术研究进展的基础上,从降低复杂度和功耗的角度,自主独立完成了维特比译码器行为级设计,并下载到Xinlix公司的Virtxell系列xcZvl000器件中,经验证功能正确。

木文主要做了以下几个方面的工作:

1、采用了软判决译码,将输入数据利用3位偏移码来表示,分析了求欧式距离的几种常用方法,从理论上对其计算过程进行了简化,方便了硬件实现。

2、对解增信删余的过程进行了详细讨论,在硬件实现上丢弃了传统的FIFO结构,节省了资源,降低了实现的复杂度。

3、为了实现低功耗设计,采取了以下措施:加比选单元采用了改进的T算法来实现,减少了不必要的操作,同时路径度量值只需要5位表示,相对于传统方法的9位大大降低了功耗;路径度量管理单元采用了串并结合的结构来实现,相比全并行结构大大降低了功耗;利用预计算方法来计算新的路径度量值,相比传统方法功耗降低了约30%。

4、为了节省存储资源,利用地址扰乱技术对路径度量的存储管理采用了原位更新的方式。本文对幸存路径管理单元结合低译码延迟和低功耗要求,提出了一利‘新型的改进分段执行HybridTraceFowrard方法,减少了存储量,并将每段存储块的长度定为6,极大的简化了译码输出过程。

5、整个设计采用virtexll系列xeZv一000一6gf256实现,最高工作频率可达231MHz,译码延时为490个时钟周期。利用xilinx公司的XST软件进行了综合并下载至xcZv1000器件中,经验证功能正确。

1 绪言 1.1 引言

DvB(nigitalVideoBroadeast)意为数字视频广播,与美国的ATsC标准以及日本的SIDB标准一起是现有的三大系列数字电视广播标准。1993年欧洲多家公司联合签署数字电视广播(DVB)备忘录,之后在日内瓦成立了欧洲DVB组织,负责并协调数字电视的各种标准的制定,目前DVB组织成员已发展到300多个,遍布世界30多个国家。它包括了卫星、有线电视、数字地面电视、SMATV、MVDS普通电视和高清晰度电视的广播与传输。现在DVB系列标准正在成为领导全球数字电视技术的世界标准。中国数字地面电视发展的关键在数据广播和高清晰度数字电视。

数字地面电视广播在中国有广大的发展空间和发展前途,随着2008年奥运会在北京的举办,数字奥运也要求实现广播电视系统从模拟向数字的技术转变,建立数字地面电视系统等,同样推动了数字电视广播在中国的快速发展。

ovB一T(oigitalVideoBoradeastingofrteerrsrtialtelevision)即地面开路数字电视广播系统,是DVB系列标准中众多系统中的一个,采用目前的开路电视特高频或甚高频频段。由于地面建筑物等对信号的多次反射以及多种噪声等多径效应的干扰,会使电视广播频率资源严重不足,为此在DVB一T中,引入COFDM处理方式。信号经过COFDM方式处理后,再灵活采用QPsK或QAM的调制方式,最后再通过上变频器进行上变频送到发射天线。这种方案具有抗多径干扰和实现移动接收等优点,在信道编码上采用以-RS为外码,卷积码为内码的级联码实现,在内码与调制器之间以及内码与外码之间各插入交织器,用来对付信道噪声及卷积译码差错事件所造成的突发差错。

在接收端对应卷积编码的译码器采用应用非常广泛的维特比译码器,它是整个内码解码的核心部分,也是最复杂和最耗费资源的部分。如何进行优化设计,降低复杂性和功耗,同时提高速度,使其能够满足高速通信系统的需要具有十分重要的意义。

1.2 差错控制编码技术及DVB一T接收系统简介

数字信息在有噪声的信道中传输时,受到噪声的影响,译码总是不可避免的。根据香农信息理论,只要使Es用0足够大,就可以达到任意小的误码率,采用差错控制编码,即信道编码技术,可以在一定的信噪比条件下有效地降低督码元,这些多余的码元与信息码元之间以某种确定的规则相互约束。也就是说,序列中信息序列的诸码元与多余码元间是相关的。接收端按照既定的规则检查信息码元与监督码元之间的关系,一旦传输过程中发生差错,则信息码元与监督码元之间的关系受到破坏,从而可以发现错误,乃至纠正错误。

差错控制编码主要有三种类型:前向纠错F(EC)、检错重发(ARQ)和混合纠错(IEc)。其中前向纠错方法接收端能根据接收序列的具体情况,猜测出发送端最有可能发送的序列。FEC不需要反馈信道,不要求检错重发,因而延时小,实时性好。

卷积码和分组码是差错控制编码的两种主要形式,在通信系统中获得广泛的应用。DVB一T系统中采用采用以RS为外码,卷积码为内码的级联码实现,在内码与调制器之间以及内码与外码之间各插入交织器,用来对付信道噪声及卷积译码差错事件所造成的突发差错。其中RS码也称为外码,码型为RS(204,188),其特点为纠正与本组(8比特为一组)有关的误码,对纠正突发Modulo一2addit一onModulo一2addition

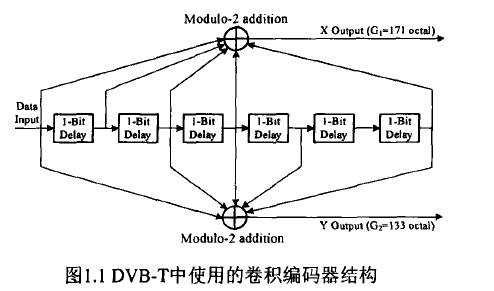

图1.1DVB一T中使用的卷积编码器结构

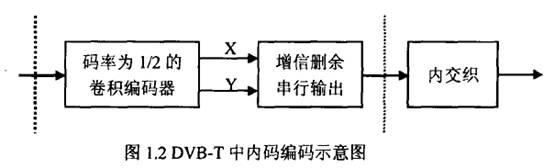

卷积编码又为内码,码率为l/2,约束长度为7,结构如图1.1所示,其两路输出经过增信删余处理后可以生成2/3,3/4,5/6和7/8多种码率,如图1.2所示,码率选择的标准是在频谱利用率和抗误码性能间权衡,卷积编码除纠正本组的误码以外,也纠正其他组的误码。

图1.2DVB一T中内码编码示意图

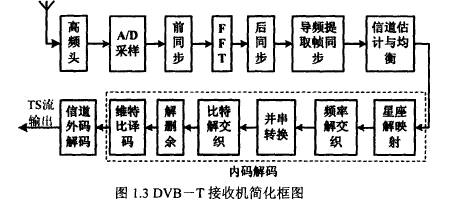

图1.3给出了DVB一T接收机的简化框图,无线信号经天线接收后由高频头将超高频信号(UHF)解调至基带信号。接下来的A心转换器将模拟信号转换成为数字信号后进行前同步。FFT处理器将时域的采样信号恢复为频域信号之后进行后同步,然后进行导频提取及信道均衡,信号再送给信道内码解码模块,

1.3 本论文的选题意义

卷积编码是一种有效的信道编码方法,是当今无线数字通信系统的一个十分重要的组成部分,在实际中广泛应用[4l。如在-wcDMA,DvB一s,DVB一,TEIEE802.n系统中都使用了卷积编码,由于其出色的纠错性能,一般在级联码中作为内码使用,为外码的有效工作而服务,以大大提高整个系统的纠错能力。

Vietbri译码算法是对卷积码在加性高斯白噪声A(WGN)信道下的最佳概率译码算法,即寻找编码器输出和译码器的经过信道后输入的最大似然函数,在实现上,通过在编码器网格图上寻找最终幸存路径可以得到译码的输出。TCM编码调制系统也采用Viethti算法译码,现在,Vietbri算法还被广泛使用在语音识别、多用户检测等领域。

在国外,对Vietbri译码器的研究己成为一个热点问题,目前Aletar、xi】inx等公司都己推出了符合EIEE标准的Vietbri译码器内核,功能非常全面,可以选择软硬判决方式、凿孔码率、约束长度等,像xinlix公司的Viethti译码器内核的约束长度、回溯长度、码率以及判决形式都是参数化的,可以选择全并行结构或者全串行结构。表1.1给出了XIlnix公司的Viterbi译码器内核在约束长度为5和7时的全并行译码的性能参数133〕。由于DsP使用上的灵活性,基于DPS开发的劝etbri译码器也得到了广泛的应用,以德州仪器公司的TMS320C6000系列DSP为例,TMS320C6000系列DSP是基于TMS320C6000平台的32位浮点DSP处理器,包含两个通用的寄存器组A和B,每组有16个32位的寄存器,时钟最高频率可达到250MHz,芯片内含8个运算功能单元,所有单元都能独立并行操作。以TM320C6701为例,它的工作频率最高为167M,最快速度可达sxl67=1336MIPs[40]。但由于DsP是通过软件来实现维特比译码算法的,在给定的维特比的译码强度下不能够满足速度的需要,限制了其在高速实时系统中的应用。另外很多公司开发了维特比译码器芯片,像AdvnaeedHardwaerAcrhietetuers公司推出的AHA4210芯片,遵照ISO/IEC规定的MPEG一11传输层协议,以B规范,维特比译码器支持可选码率1/2,2/3,3/4,5/6,6/7,7/8,维特比译码数据速率可达到62Mb/[s/2],性能强大,但在实际应用中很多功能用不到,可配置性差。此外很多PI核或芯片都基于传统的维特比译码算法,没有针对具体要求改进的算法和结构,所以性能一般,而随着通信系统的发展要求更高的速度和更低的功耗,使得开发专用的高速低耗的维特比译码器成为必要。

1.4 本论文的研究内容

. 本论文将对几个关键模块进行算法和结构上的优化,提高整个译码器的工作速度,同时在在功耗上进行优化,在保证速度的前提下,尽量少的消耗功耗。