在FPGA内采用等精度测频法测出频率和周期,可实现对有效值为0.005V~5V,频率范围1Hz~35MHz 信号的频率、周期的测量。用计数法测出相位差,可实现对有效值0.5V~5V,频率10Hz~100KHz 信号的相位差测量。系统功能由按键控制,可对测量结果实时显示,人机交互界面友好,达到了较好的性能指标。

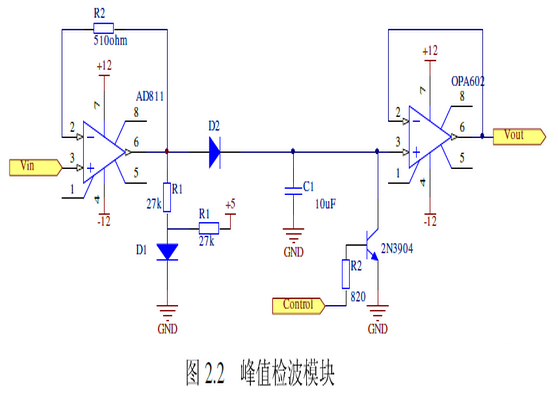

峰值检波模块

在进入模拟开关之前,需要进行峰值检波,通过测得的信号的幅值确定模拟开关的通道。峰值检波电路是由二极管电路和电压跟随器组成,其工作原理为:当输入电压正半周通过时,检波管D2导通,对电容C1充电,直到到达其峰值。三极管的基极由单片机控制,产生10us 的高电平使电容放电,以减少前一频率测量对后一频率测量的影响,提高幅值测量精度。其中D1处于常导通状态,用以补偿D2 上造成的压降。电容C1 的取值需根据被测信号的频率合适的选取,此电路中的二极管使用高频二极管,可大大提高测量范围的频率上限。其电路图如图2.2 所示。

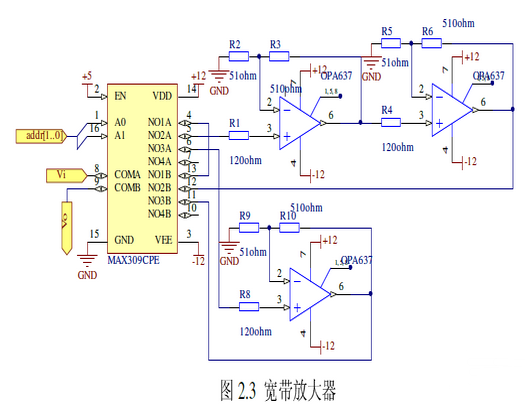

宽带通道放大器分析

为了检测有效值0.005V~ 5V的信号(即Vp_p 为0.014V~14V)的频率,而高频比较器TL3116能检测到的输入信号的最小幅度Vp_p=0.8V,因此需要对信号进行程控放大。当测得的信号峰峰值Vp_p小于0.1V 时,设定放大倍数为120,当0.1V~1V 时设定放大倍数为10,当Vp_p大于1V时,设定放大倍数为1。以MAX309为模拟开关,用OPA637接成一级同相放大器进行10倍增益放大。用两级OPA637级联进行120倍放大。其原理图如图2.3。

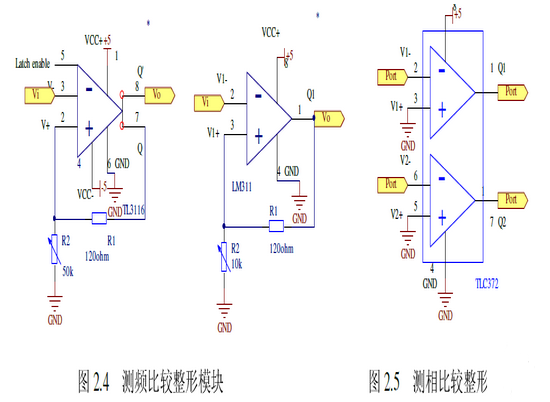

比较整形电路

在测频、测周部分,由于我们没有带宽由1Hz 到35MHz 的比较器,所以采用分段处理的方法实现整个频带的测量,高频部分用TI公司的TL3116实现,低频部分采用LM311。为抑制干扰引起的误翻转,我们采取了带正反馈的滞回比较电路的形式。

在反相输入方式时,其正向阈值电压,对应比较后信号的下降沿。负向阈值电平为0V,对应于比较后信号的上升沿。故输出信号的上升沿仍属过零比较。测相的两路信号经过整形,要使产生的额外相差最小,必须保证两路通道参数的一致性,选用TI 公司的双路比较器TLC372。

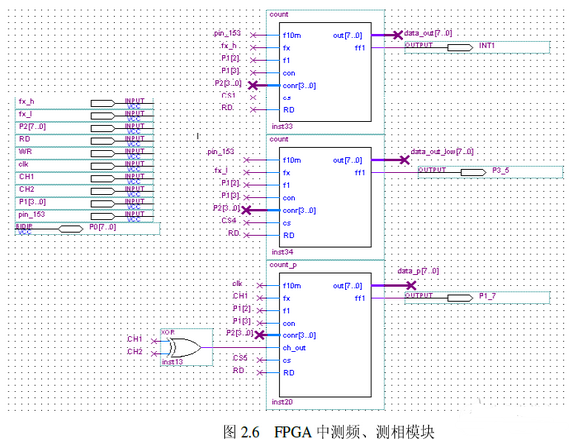

FPGA 模块

本系统采用数字方法在FPGA 内部进行频率和相位差的测量。其电路图如图2.6 所示。其中fx_h 和fx_l 分别为高频信号和低频信号输入端。CH1 和CH2分别为两路相位信号如数端。