介绍了一种基于Verilog-HDL描述的多功能步进电机控制芯片的可综合方案,该方案可方便地构成两相双极或四相单极步进电机的控制系统。外接元件极少,只需给定时钟、转向以及工作模式信号,就可使系统工作。该方案采用模块化设计,可扩展性好,为步进电机的低成本控制提供了一种新的思路和实现方法。

关键词:ispLSI器件,Verilog┐HDL,四相步进电机

1引言

步进电机是一种将数字信号转换为角位移或线性位移的控制驱动装置。它的速度和控制脉冲严格同步,响应速度极快,有较高的重复定位精度,大量应用在精密控制的场合。

常用的步进电机控制系统,采用微机控制,用软件实现其步进脉冲的产生。这种方法程序量大,占用CPU时间较多,限制了步进电机速度的进一步提高,而且软件方式的抗干扰性能较差,在EMI较严重的场合其可靠性不如纯硬件电路。在硬件中,环形分配器逻辑关系复杂,用传统的分立元件实现,电路规模大,连接线复杂,灵活性差,功耗较大,其系统可靠性也不尽人意。

ISP(In-system Programming)技术是由Lattice半导体公司首先提出的一种新技术,它以大规模可编程逻辑器件为核心,具有对电子器件、电路板、甚至整个电子系统的逻辑和功能进行动态重组的能力。它可以取代几乎所有的74系列芯片,可根据需要自主配置其硬件资源,电路功耗低,是硬件软件化的关键。

传统的电子系统设计,多采用原理图输入,过程复杂,只能从结构上对电路进行描述,设计灵活性差。现代的EDA/ESDA设计工具,均采用HDL(HardwareDescription Language)作为设计输入,它可以从电路行为级开始建模,设计效率高,灵活性强。VHDL是国际上第一个标准化的HDL(IEEE-1076),而VerilogHDL是1995年实现标准化的新HDL标准(IEEE-1364),其描述方式接近C语言,编写风格简明,代码效率高,并支持模拟仿真。用它描述的步进电机控制系统,结构明晰,可扩展性好。经综合生成网表下载后就可生成硬件电路。

2芯片设计思想概述

2.1总体架构

整个芯片采用模块化设计方式,TOP-DOWN的设计方法。

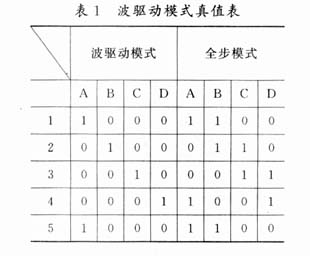

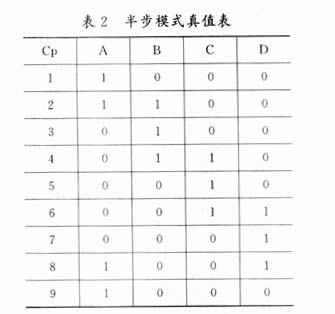

该芯片共有三种驱动工作模式:波驱动(Wave)模式、半步驱动(Half Step)式,全步模式。

波驱动模式也称四相单四拍工作模式,电机的四个绕组分别轮流通电;全步模式也称四相双四拍工作模式,每一时刻,电机总有两相绕组同时通电;半步模式也称四相八拍控制方式。这种工作模式下,步进电机每一步的步距仅为全步模式的一半,常用于精密定位。

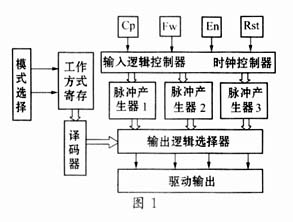

上述三种工作模式由芯片的模式输入(mode)指定切换。芯片上还配置正反转输出控制(fw),复位控制(rst)和紧急停车控制(en)。芯片结构示意图见图1。

2.2各部分功能分析

脉冲产生部分:该部分实际上是一系列特殊的计数器,每当CP时钟的上升沿到来时,计数器输出下一状态,驱动步进电机。

时钟控制部分:该部分实际上是带输入控制的同相门。当en=0时,门被封锁,输出高阻态;en=1时,门打开,CP通过该门输入。该部分可用作停车控制。与MCU接口时,CP可由单独的振荡电路提供,MCU不用干预CP的产生,可节省MCU时间。

输入输出逻辑控制:该部分包括输出选择,模式选择,复位控制,方向控制,全桥驱动抑制信号控制。这一部分在设计的顶层模块中描述。

3各模块的设计

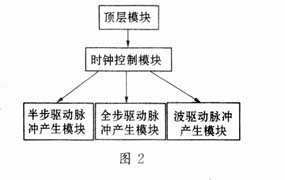

根据各部分的功能,将全系统分为脉冲产生模块、时钟控制模块和顶层模块三部分。

各模块关系如图2所示。

3.1脉冲产生电路的设计

根据步进电机三种不同驱动方式的特点,列出驱动口的真值表,利用状态机的方法建立相应模型。

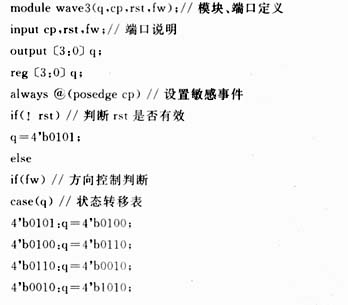

在Verilog语言中,可以将时钟信号上升沿设置为触发的敏感事件,用case语句实现状态的转移,由if-else检测正反转控制信号和rst信号。每当cp的上升沿到来时,电路输出下一状态。fw=1时,电机正转,fw=0反转,rst=0时输出复位,rst=1时正常工作。每个Verilog模块以module开头,以endmodule结束。

下面给出半步驱动模式源程序:

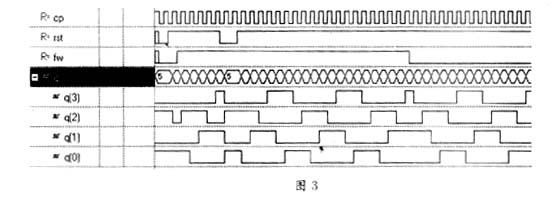

以上程序是否满足设计功能要求呢?为此,我们编写了测试程序,并在Active-HDL仿真平台下进行功能验证。由于各模块功能引脚类似,下面只给出半步驱

其仿真波形如图3所示。

由仿真波形可见,满足设计的功能要求。

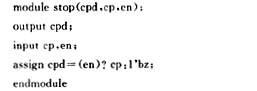

3.2时钟控制模块设计

本电路是时钟信号传输的通道,电路时钟输出端cpd接至脉冲输入cp端。当en=1时,系统正常工作,cpd=cp;en=0时,cpd输出高阻态,无时钟脉冲输入到脉冲产生器。en可作为紧急停车控制。

源程序如下:

3.3驱动抑制信号的设计

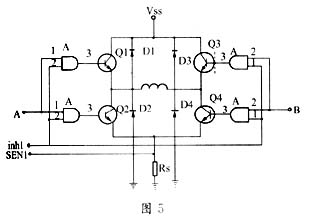

在本设计中,输出驱动采用L298高压大电流双H桥芯片,输入为逻辑电平,具有输入抑制功能。下面以两相双极步进电机接法来说明驱动抑制信号的作用。

L298可接入Rs作为电流反馈。正常工作时(A=1,B=0),电流通路为Vss-Q1-L-Q4-Vdd。由驱动波形分析可知,在波驱动和半步模式下,当换流时(A=B=0),Q4没有关断,续流通道Vdd-D2-L-Q4-Rs-Vdd,这样不仅会延长绕组电流衰减时间,还会增大Rs上的功耗。为解决这一矛盾,特引入抑制信号inh。此时若使抑制信号inh=0,就可强制Q1、Q2、Q3、Q4全部关断,此时,换流通道Vdd-D2-D3-Vss。当抑制信号有效时,还能防止信号串扰。

图5是L298其中一个全桥的示意图。其中,A、B两路信号分别用于控制两个桥臂,当A、B两路信号不同时为0时,驱动抑制inh=1,不产生抑制作用;当A=B=0时,inh=0,产生抑制。

由上述分析可知:inh1=A+B,inh2=C+D(inh1,inh2分别为左右两桥的驱动抑制信号)。

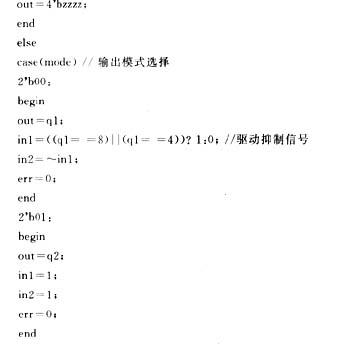

3.4顶层模块设计

顶层模块中包括有输出选择,驱动模式选择,复位控制,方向控制及全桥驱动抑制信号控制。因此,根据系统控制要求,调用上述所有的模块,是顶层模块的主要任务。当mode=00时,输出为波驱动模式,mode=01时,输出为全步模式,mode=10时,输出为半步模式,mode=11时,err=1,报错,输出为高阻态。抑制输出为in1、in2,全步模式时in1、in2输出均为1。

顶层设计源程序如下:

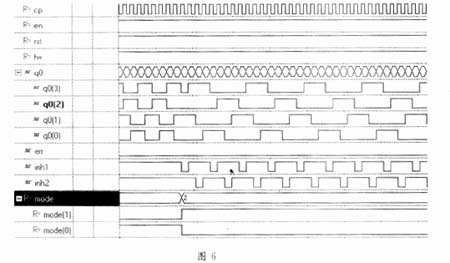

根据顶层模块的功能,我们设计了该模块的测试程序,并进行了仿真。由波形分析可见,完全达到设计要求。下面给出mode=10时,半步驱动的输出波形。顶层仿真波形如下:

由于各模块的独立性,在物理测试过程中可对各模块分开综合调试,以此确保硬件电路能同时满足预期的功能和逻辑约束条件。本设计使用Syplify作为综合器,生成edif文件后,用lattice的ispEXPERTComplier生成jed文件,再用ispDCD配合JTAG电缆下载至lattice ispLSI1032中进行硬件电路验证。

4结束语

本设计综合后下载于ispLSI1032,并以此构成步进电机控制系统,使用ASTROSYN 12V步进电机进行了试验。试验中由89C2051单片机产生模式选择信号,由555组成振荡电路,产生1.5kHz时钟信号。试验证明,此系统功能满足设计要求,控制灵活,工

作稳定,电机无失步现象。

参考文献

1王金明,杨吉斌编著.数字系统设计与Verilog HDL(第1版).北京:电子工业出版社,1998,1

2杨渝钦主编.控制电机(第1版).北京:机械工业出版社,2001