与门(英语:AND gate)又称“与电路”、逻辑“积”、逻辑“与”电路。是执行“与”运算的基本逻辑门电路。有多个输入端,一个输出端。当所有的输入同时为高电平(逻辑1)时,输出才为高电平,否则输出为低电平(逻辑0)。

中文名:与门

外文名:AND gate

含 义:所有条件必须具备。

表达式:F=A·B

所属范围:逻辑门

别 名:与电路、逻辑积、逻辑与电路

功 能:执行“与”运算的基本逻辑门电路

应用学科:物理等

适用领域:电路、逻辑等

基本功能

与门是实现逻辑“乘”运算的电路,有两个以上输入端,一个输出端(一般电路都只有一个输出端,ECL电路则有二个输出端)。只有当所有输入端都是高电平(逻辑“1”)时,该电路输出才是高电平(逻辑“1”),否则输出为低电平(逻辑“0”)。 其二输入与门的数学逻辑表达式:Y = AB,对应的真值表如下:

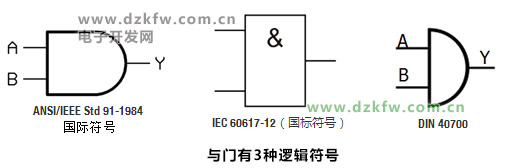

逻辑符号

与门有3种逻辑符号,包括:形状特征型符号(ANSI/IEEEStd 91-1984)、IEC矩形国标符号(IEC 60617-12)、DIN符号(DIN 40700)。

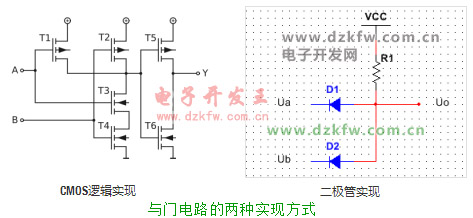

实现

与门的实现方法包括使用CMOS逻辑、NMOS逻辑、PMOS逻辑以及二极管实现等。

以二极管实现为例,与门的实现原理为:

如图:为二极管与门电路,Vcc = 5v,R1 = 3K9, 假设3v及以上代表高电平,0.7及以下代表低电平,

下面根据图中情况具体分析一下,

1. Ua=Ub=0v时,D1,D2正向偏置,两个二极管均会导通,此时Uo为电位为0.7v.,输出为低电平

2.当Ua,Ub一高一低时,不妨假设Ua = 3v,Ub = 0v,这时我们不妨先从D2开始分析,

D2会导通,导通后D2压降将会被限制在0.7v,那么D1由于右边是0.7v左边是3v所以会反向偏置而截止,因此最后Uo为0.7v低电平输出,这里也可以从D1开始分析,如果D1导通,那么Uo应当为3.7v,

此时D2将导通,那么D2导通,压降又会变回0.7,最终状态Uo仍然是0.7v.输出低电平,此时D1马上截止。

3. Va=Vb=3v,这个情况很好理解, D1,D2都会正偏,Uy被限定在3.7V.

总结(借用个定义):通常二极管导通之后,如果其阴极电位是不变的,那么就把它的阳极电位固定在比阴极高0.7V的电位上;如果其阳极电位是不变的,那么就把它的阴极电位固定在比阳极低0.7V的电位上,人们把导通后二极管的这种作用叫做钳位。(特别说明:压差大的二极管先导通,先钳位,先导通的二极管具有电路控制权)

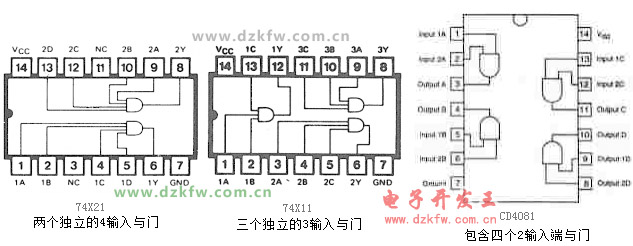

集成电路

与门是基本的逻辑门,因此在TTL和CMOS集成电路中都是可以使用的。标准的74系列CMOS集成电路有74X08、74X09(OC),包含四个独立的2输入与门;74X11,包含三个独立的3输入与门;74X21,包含两个独立的4输入与门。CD4000系列集成电路有:CD4081,包含四个2输入端与门;CD4082,包含两个4输入端与门。 引脚分配如下: