移位寄存器不但可以寄存数码,而且在移位脉冲作用下,寄存器中的数码可根据需要向左或向右移动。移位寄存器也是数字系统和计算机中应用很广泛的基本逻辑部件。

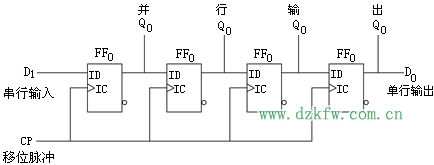

图1所示电路是由边沿D触发器组成的4位移位寄存器。

由图1可知,由第一个D触发器FF0的输入端接收输入信号,其余的每个触发器的输入端均与前一个触发器的输出端相连。各触发器的时钟脉冲控制端与同一个时钟脉冲CP信号相连,因此各触发器的触发时刻相同,都是CP脉冲的上升沿。

下面以4位二进制代码1101为例,说明图1所示移位寄存器的寄存过程。

二进制代码1101以串行的方式从串行输入端DI依次输入。设各触发器的初始状态为零,即Q3Q2Q1Q0=0000。

|

| 图1 由D触发器组成的4位移位寄存器 |

首先,将第一个二进制码“1”输入串行输入端DI。当移位脉冲CP的第一个上升沿到达时,个触发器将各自的输入端状态传输到输出端。由于从CP脉冲的上升沿到达开始到各触发器次态的建立需要一段传输延时时间,因此当CP脉冲的上升沿同时作用于各触发器时,各触发器输入端的状态还没有改变。于是FF3按Q2原来的状态触发,FF2按Q1原来的状态触发,FF1按Q0原来的状态触发,FF0按串行输入端D1的状态触发。因此,当CP的第一个上升沿到达后,各触发器的状态变为Q3Q2Q1Q0=0001。

同理,将第二个二进制数码“1”送入串行输入端D1,当CP的第二个上升沿到达时,各触发器的状态变为Q3Q2Q1Q0=0011。以此类推,当第4个移位脉冲过后,将这4个二进制代码储存到了4个触发器的输入端Q3Q2Q1Q0=1101。

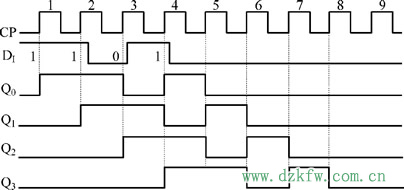

移位数据寄存情况如表1所示。也可以用波形图的形式表示移位寄存器的数据寄存情况,如图2所示。

| 表1 移位寄存器的移位寄存过程 |

| CP脉冲 | 串行输入DI | Q3 | Q2 | Q1 | Q4 |

| 0 | × | 0 | 0 | 0 | 0 |

| 1 | 1 | 0 | 0 | 0 | 1 |

| 2 | 1 | 0 | 0 | 1 | 1 |

| 3 | 0 | 0 | 1 | 1 | 0 |

| 4 | 1 | 1 | 1 | 0 | 1 |

|

| 图2 图1电路的波形图 |

从图6-5-3所示的波形图可以看出,经过4个CP脉冲后,串行输入的4位二进制代码全部已入了移位寄存器中,同时可以从4个触发器的输出端同时输出这4为二进制代码。如果继续加入4个CP脉冲,则可以从串行输入-并行输出和串行输出入-串行输出。由于在移位脉冲的作用下,二进制代码在移位寄存器中依次右移,所以又称为右移移位寄存器。当移位寄存器的电路实现的是在移位脉冲的作用下,二进制代码在移位寄存器中依次左移,这种寄存器称为左移移位寄存器。

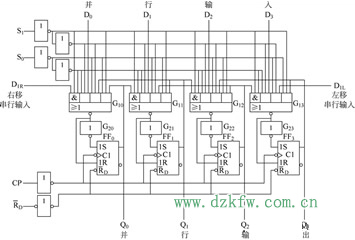

为了便于扩展移位寄存器的功能和增加使用的灵活性,在定型生产的移位寄存器集成电路上有的又附加了左移、右移控制,并行数据输入、保持、异步置零(复位)等功能。图3所示为4位双向移位寄存器74LS194的逻辑电路和图形符号。

|

|

| 图3(a) 逻辑图 | 图3(b) 图形符号 |

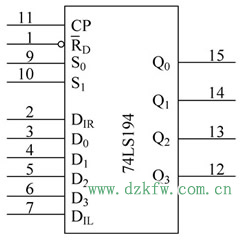

由图3所示,双向移位寄存器74LS194由4个RS触发器和输入控制电路组成。DIR为数据右移串行输入端,DIL为数据左移串行输入端,D0~D3为数据并行输入端,Q0~Q3为数据并行输出端,同时Q3还可以作为数据串行输出端,CP为移位脉冲控制端![]() 为清零端,移位寄存器正常工作时该端置“1”,S0、S1为双向移位寄存器的工作状态控制端。

为清零端,移位寄存器正常工作时该端置“1”,S0、S1为双向移位寄存器的工作状态控制端。

74LS194既可以实现串行输入,也可以并行输入;既可以实现串行输出,也可以并行输出,在串行寄存方式中,既可以实现右移寄存,也可以实现左移寄存,还可以保持数据不变。74LS194双向移位寄存器的这些工作状态都是由控制端S0、S1实现的,如表1所示。表1称为74S194的逻辑功能表。

| 表1 74LS194的逻辑功能表 |

| S1 | S4 | 工作状态 | |

| 0 | × | × | 置零 |

| 1 | 0 | 0 | 保持 |

| 1 | 0 | 1 | 右移 |

| 1 | 1 | 0 | 左移 |

| 1 | 1 | 1 | 并行输入 |

当S1=S0=0时,移位寄存器处于数据保持状态。此时不论输入端和移位脉冲输入端有何变化,移位寄存器各输出端的状态保持不变。

当S1=0,S0=1时,移位寄存器保持右移寄存状态。随着位移脉冲的到来,右移串行输入端DIR的数据依次寄存到寄存器中,并且移位寄存器中的数据依次右移。

当S1=1,S0=0时,移位寄存器处于左移寄存状态。随着移位脉冲的到来,左移串行输入端DIL的数据依次寄存到寄存器中,并且移位寄存器中的数据依次左移。

当S1=1,S0=1时,位移寄存器处于并行输入寄存状态。此时串行输入端的数据不起任何作用。当移位脉冲CP来一个脉冲时,寄存器将并行输入端D0~D3的数据并行输入到并行输出端Q0~Q3。

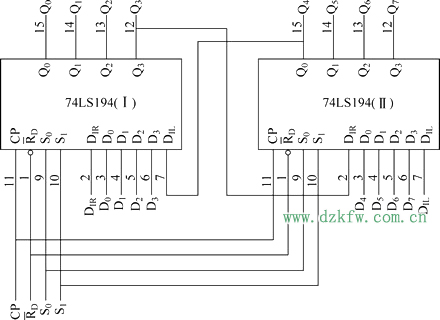

例1 用两片4位双向移位寄存器74LS194接成一个8位双向移位寄存器。

解 所要涉及的8位双向移位寄存器需要完成8位二制数据的寄存,因此需要由两片4位双向移位寄存器74LS194组成。同时,8位双向移位寄存器应具备4位双向移位寄存器所有的逻辑功能,即能实现并行输入、左移寄存、右移寄存、数据保持和异步清零等功能。

如图4所示,通过分析,将两片4位双向移位寄存器的输入和输出同时作为8位双向移位寄存器的输入和输出。将74LS194(I)的右移串行输入端作为8位双向移位寄存器的右移串行输入端,同时将74LS194(I)的串行输出端与右侧74LS194(II)的右移串行输入端相连。同样,将74LS194(II)的左移输入端作为8位双向移位寄存器的左移串行输出端,同时将74LS194(II)的串行输出端与74LS194(I)的左移串行输入端相连。将两片4位双向移位寄存器的移位脉冲输入端、清零端和工作状态输入端分别相连。这样,就实现了用两片4位双向移位寄存器74LS19474LS194接成一个8位双向移位寄存器。

|

| 图4 例1的电路图 |